java加密算法

ratio-test

题解

激活函数

SylixOS

二分法

web大作业

Hash

java8新特性

Hudi

快速幂算法

PORT和PID区别

遥感数据处理

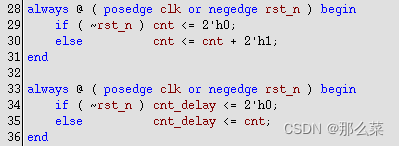

定时器

金融学

pcb工艺

51单片机

网赚项目

shell入门

optee

SystemVerilog

2024/4/12 5:27:33【sv中枚举类型与字符串语法学习】

文章目录枚举基本语法类型转换枚举类型内置方法字符串内置方法枚举

基本语法

枚举类型可以用来声明一组整型的命名常量,定义具有强类型的枚举变量。枚举类型还可以使用枚举名字而不是枚举值来方便地引用或显示。当没有指定数据类型的时候,缺省的数据类…

verilog中函数用法

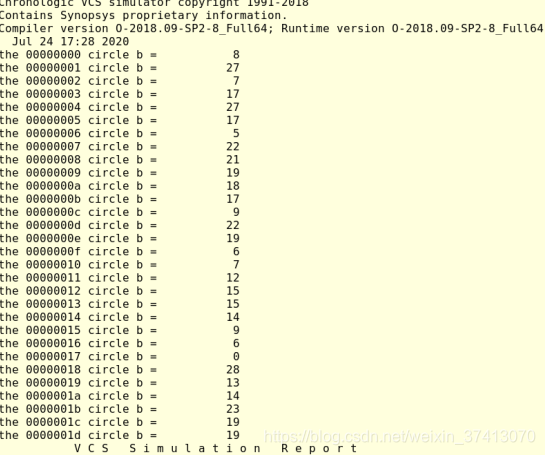

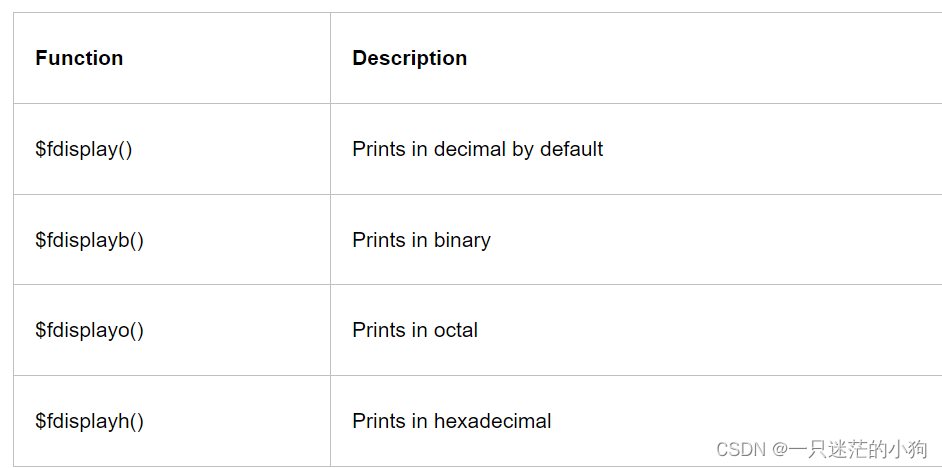

verilog中函数用法读写文件常用1.1打开文件1.2读写文件2执行系统命令读写文件常用

1.1打开文件

$fopen打开文件,用法如下:

1. $fopen("<文件名>");

2. <句柄>$fopen(“<文件名>”);用法1自然无须多…

systemverilog中的参数传递——ref、input、output

systemverilog中的参数传递——ref、input、output1 静态数组作为参数1.1 input1.2 output1.3 ref2 动态数组或队列作为参数3 类作为参数4 原文链接1 静态数组作为参数

sv中的静态数组、动态数组、队列都是用一块内存存放,而他们的名字作为该内存的地址,…

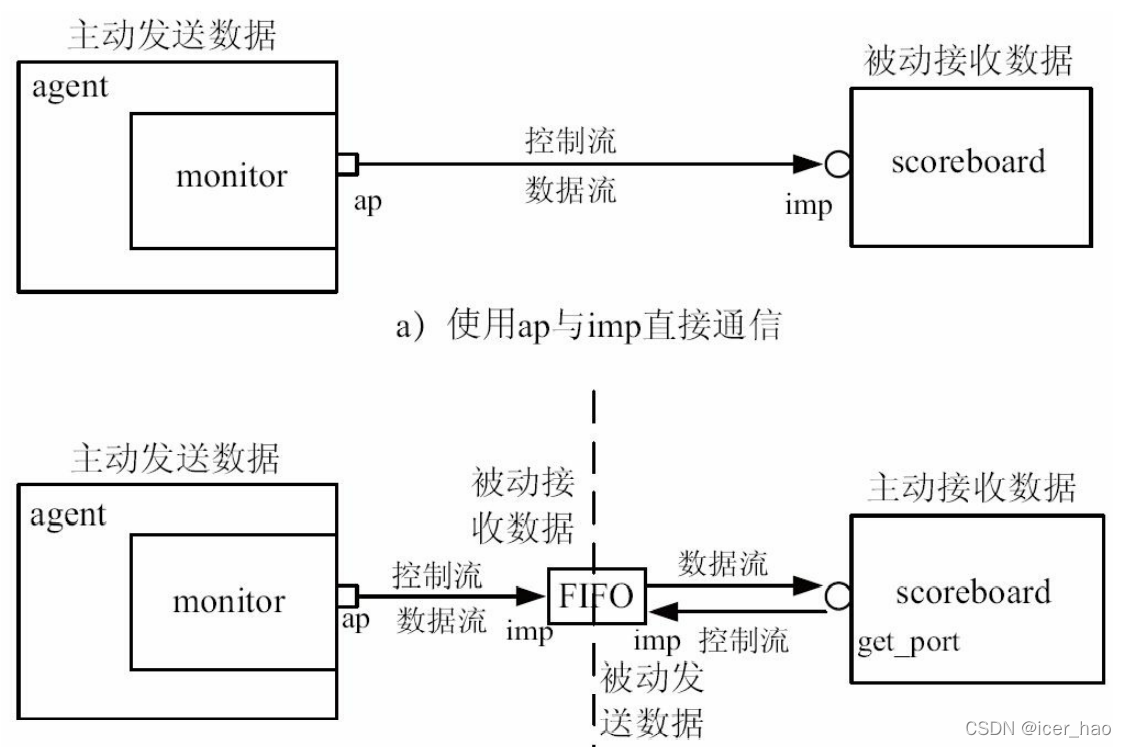

uvm_analysis通信端口学习

文章目录前言与blocking_port 和blocking_export区别使用实例uvm_analysis_imp_decl宏的用法利用fifo通信前言

UVM实现通信的TLM机制中通常有put,get等术语,put操作是指通信的发起者A把一个transaction发送给B,而get操作指A向B索取一个trans…

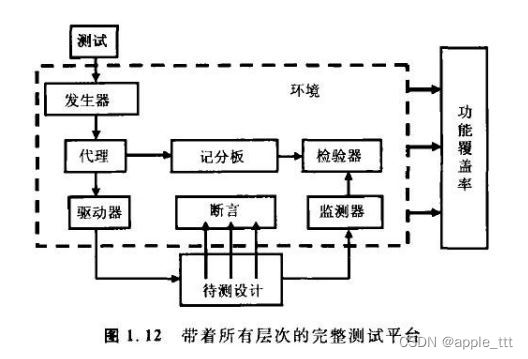

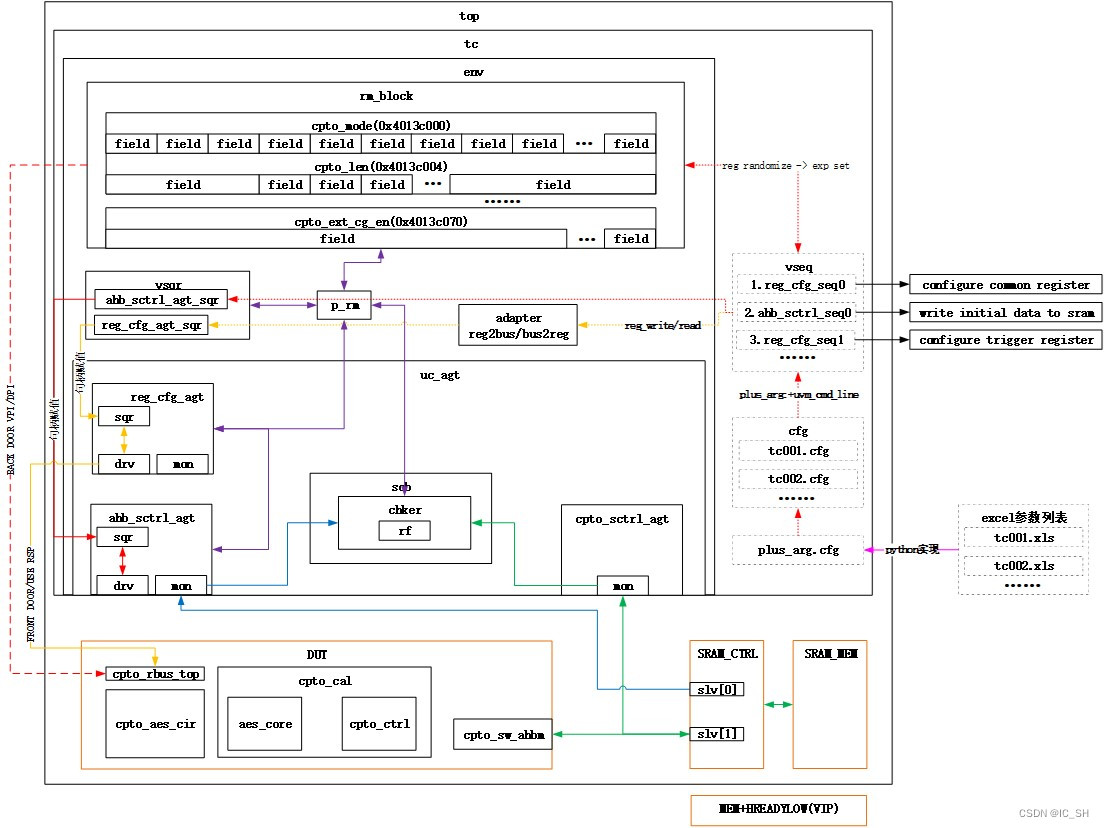

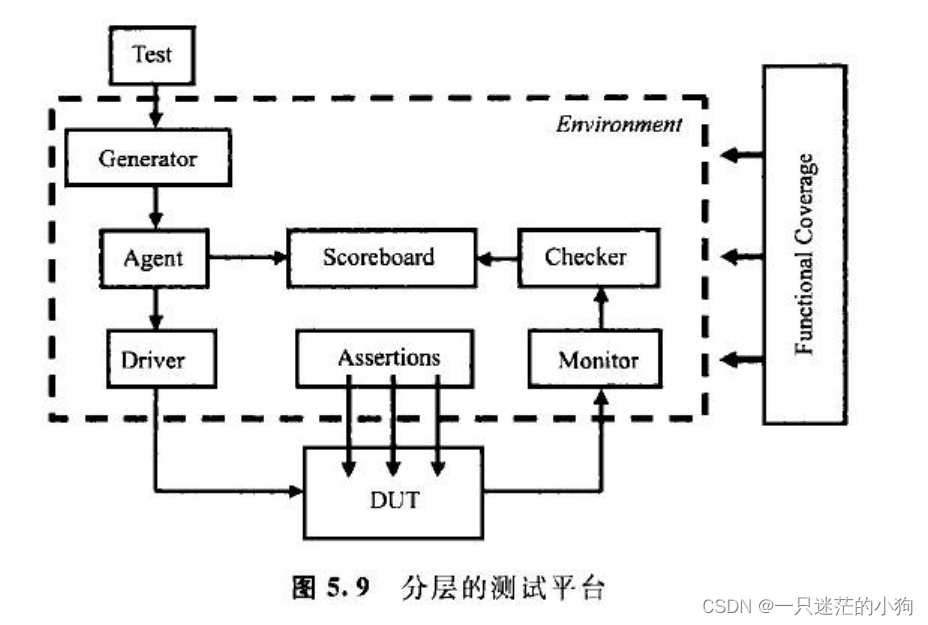

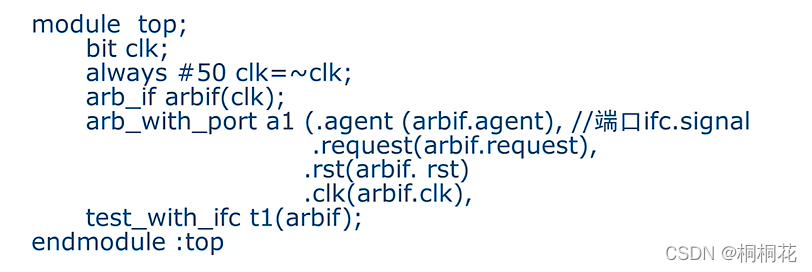

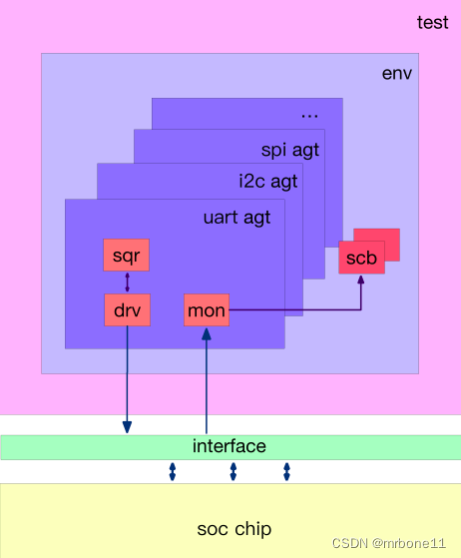

SystemVerilog学习 (6)——验证平台

一、概述 测试平台(Testbench)是整个验证系统的总称。它包含了验证系统的各个组件、组件之间的互联关系,测试平台的配置与控制等, 从更系统的意义来讲,它还包括编译仿真的流程、结果分析报告和覆盖率检查等。 从狭义上…

UVM中uvm_config_db机制背后的大功臣

1. 前言

本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。这样的数据库允许我们以不同的名称存储不同的配置设置,这些配置可以在需要时潜在地配置TB组件…

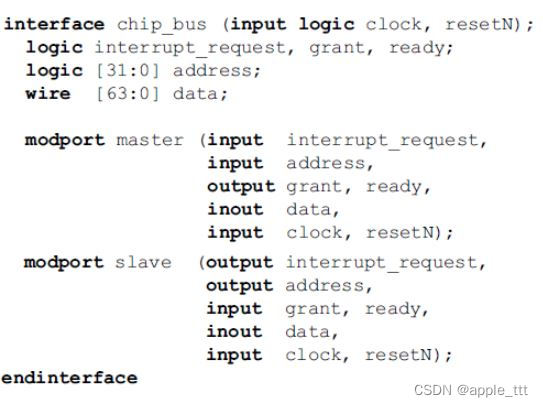

IEEE Standard for SystemVerilog—Chapter25.5 Modports

25.5 Modports 为了限制模块内的接口访问,有一些modport列表,其中包含在接口内声明的方向。关键字modport表示方向是在模块内部声明的。

interface i2;wire a, b, c, d;modport master (input a, b, output c, d);modport slave (output a, b, input c,…

关于句柄与new函数的简单理解

前言

在实际应用中,经常会遇到句柄和new函数,但是对二者的意义一直没有搞明白。通过查阅资料,谈谈个人对句柄与new函数的理解,有错误还请各位批评指正!

句柄

通常以类class的名字声明一个句柄,如 driver…

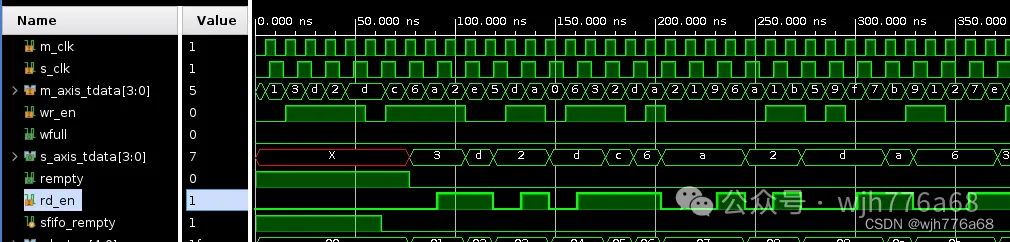

【FIFO】Standard / FWFT FIFO设计实现(二)——异步时钟

标准FIFO 异步FIFO需要使用格雷码同步读写信号,可参考牛客异步FIFO例题,不同于牛客例题之处在于FIFO读空信号置位与FIFO最后一个有效数据输出在同一个周期,与Xilinx FIFO一致。核心代码如下: logic [FIFO_DEPTH_WIDTH : 0] rd_ptr…

uvm白皮书练习_ch2_ch222加入factory机制

uvm白皮书练习_ch2_ch222只有factory机制 factory机制的实现被集成在了一个宏中:uvm_component_utils。 这个宏所做的事情非常多,其中之一就是将my_driver登记在UVM内部的一张表中,这张表是factory功能实现的基础。

自动创建一个类的实例并调…

Systemverilog中$cast()的使用

Systemverilog中$cast()的使用

1 静态转换

SV类型转换分两种方法,一种叫静态类型转换,另一种称之为动态类型转换。静态类型转换的语法类似为:

int a 2;

real b;

b real(a); 这种类型()的静态类型转换,一般不检查转换是否…

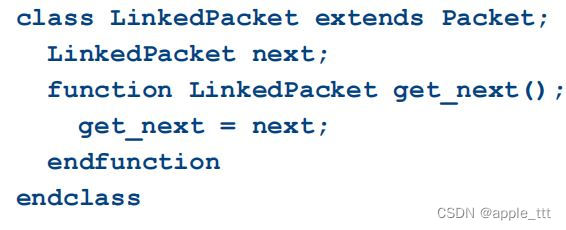

SV中的Class知识

SV中的Class知识0. 基础1. static2. shallow copy3. deep copy5. parameterized class6. 继承7. 多态(polymorphism)8. 修改成员函数9. super10. casting11. 公有和私有12. 抽象类(abstract class)12. 域分辨符::13. External14. …

前端设计低功耗处理手段

一般考虑低功耗问题,主要是从系统供电、使用问题、性能问题、成本考虑、可靠性、竞品等几个方面展开。 低功耗设计方法有很多:系统级而言,有动态调压调频(DVFS)、电源门控(Power Gating)、时钟门…

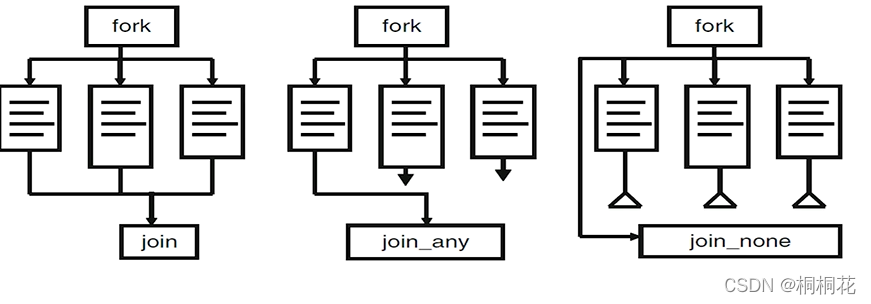

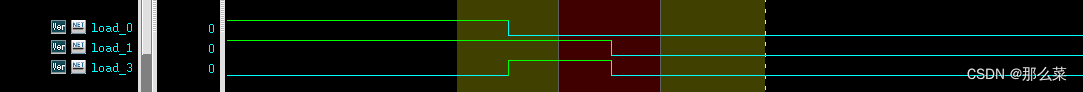

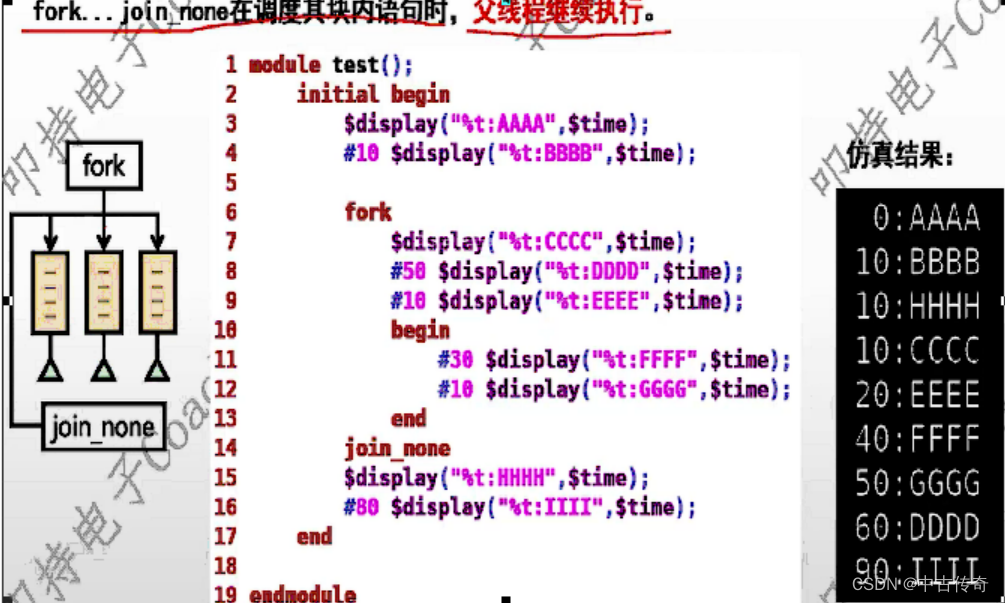

[SV]SystemVerilog线程之fork...join专题

SystemVerilog线程之fork...join专题 Q:fork-join_none开辟的线程在外部任务退出后也会结束吗? A:后台线程不会结束,任何由fork开辟的线程(join、join_any、join_none),无论其外部任务ÿ…

SystemVerilog基础:并行块fork-join、join_any、join_none(二)

相关阅读

SystemVerilog基础https://blog.csdn.net/weixin_45791458/category_12517449.html 在第一节中,我们讨论了并行块中的fork-join块和fork-join_any块,了解了它们的差异,本文将继续讨论fork-join_none块的使用。 fork-join_none并行块…

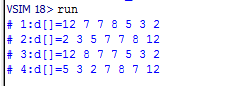

【SystemVerilog】数据类型(3)数组的方法

目录

一、数组缩减方法

二、数组定位方法

三、数组排序方法 SV提供了很多数组的方法,可用于任何一种非合并的数组类型,包括定宽数组、动态数组、队列和关联数组。这些方法有繁有简,简单的如求当前数组的大小,复杂的如对数组排序…

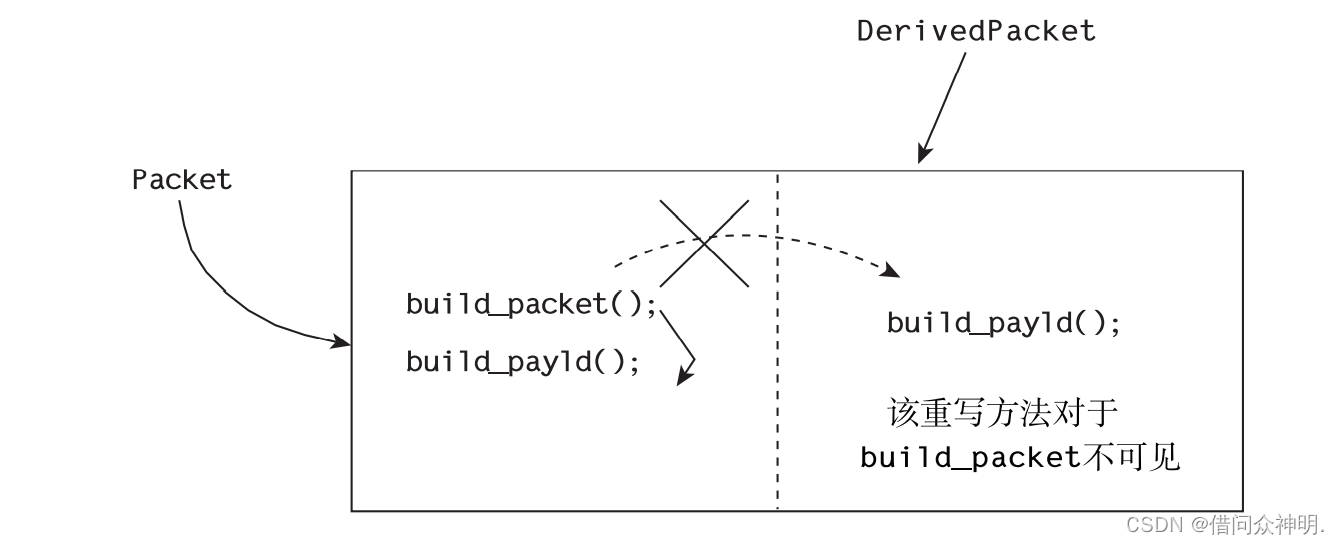

【sv中的继承与多态】

文章目录继承多态虚方法实现多态步骤继承

在验证的过程中,经常会有新的测试用例被添加进来,而且需要对原有的验证平台进行改进,特殊的测试用例经常会要求验证平台添加特定的功能。在过程化编程语言中,这要求修改原来的代码并且有…

Systemverilog中关于@和wait的区别

本文转载自Systemverilog中和wait區別及應用案例分析 Systemverilog中和wait區別及應用案例分析 前言:在SystemVerilog中,用来触发事件时,使用->;用来等待事件使用或者wait。那么和wait有什么区别呢?在Verilog中当一…

模块(module), 程序块(program)的区别

文章目录moduleprogram注意点区别module

在verilog中,模块可以用来描述从简单的门元件到复杂的系统 (例如一个微处理器)的任何一种硬件电路。模块除了可以为硬件建模外,也可以用来封装验证平台,在模块内部,…

【$fopen函数的用法】

文章目录语法介绍uvm中的用法语法介绍 $fopen函数的功能是使用给定的模式 mode 打开 filename 所指向的文件。文件顺利打开后,指向该流的文件句柄就会被返回。如果文件打开失败则返回 0。 $fopen函数格式如下: <file_desc> $fopen("", …

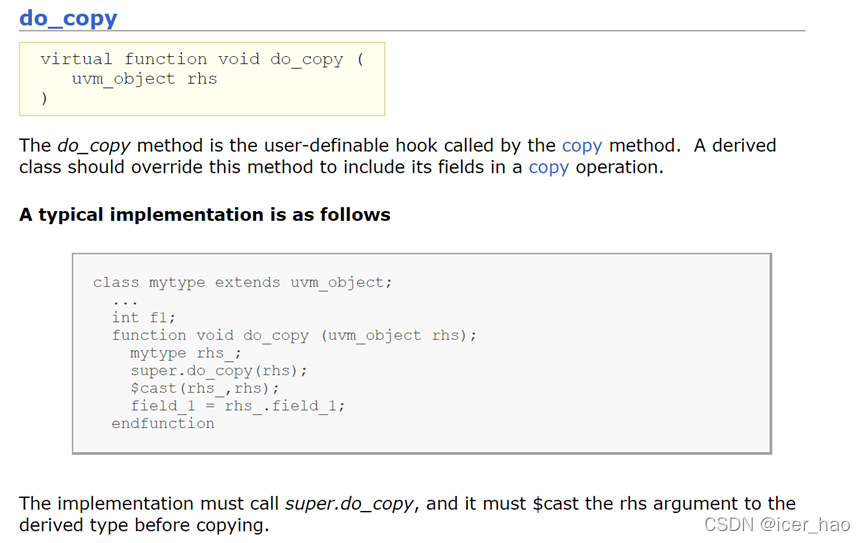

【sv中浅拷贝与深拷贝】

文章目录前言浅拷贝(shallow copy)深复制 (deep_copy)UVM中实现深复制的方法前言 本文通过实际代码编译介绍了sv中浅复制和深复制的区别 浅拷贝(shallow copy)

先给出实际代码

module shallow_copy();class A;integer j 5;endc…

#systemverilog# 之 event region 和 timeslot 仿真调度(六)疑惑寄存器采样吗

一 象征性啰嗦

想必大家在刚开始尝试写Verilig HDL代码的时候,都是参考一些列参考代码,有些来自于参考书,有些来自于网上大牛的笔记,甚至有写来自于某宝FPGA开发板的授权代码。我还记得自己当时第一次写代码,参考的是一款Altera 芯片,结合Quartus 开发软件, 在上面练习…

uvm_event 的使用

uvm_event 的使用

uvm_event可以用来在不同的组件里实现同步的作用。

class exm_driver extends uvm_driver #(data_transaction)uvm_event frame_event...function void build_phase(uvm_phase phase)super.build_phase(phase);frame_event uvm_e…

svn 问题之右键没有checkout 选项

svn 问题之右键没有checkout 选项1.原因2.解决办法3.参考1.原因

之所以出现这种问题,是因为曾经在当前地址checkout 过文件,当前地址受到svn的控制,svn不允许在当前地址下再嵌套另外一个svn库。 换个不受控的文件夹点右键,就会发…

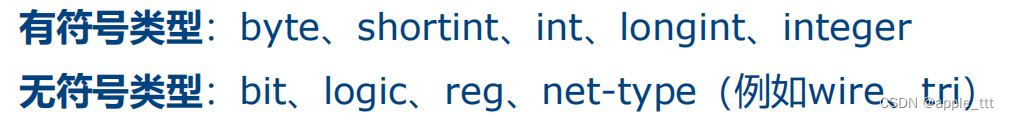

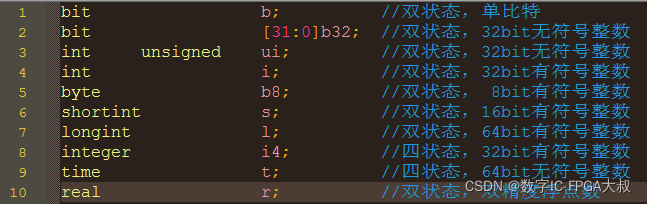

SystemVerilog学习(2)——数据类型

一、概述 和Verilog相比,SV提供了很多改进的数据结构。它们具有如下的优点:

双状态数据类型:更好的性能,更低的内存消耗队列、动态和关联数组:减少内存消耗,自带搜索和分类功能类和结构:支持抽…

uvm白皮书练习_ch2_ch223_加入objection机制

UVM中通过objection机制来控制验证平台的关闭。 在每个phase中,UVM会检查是否有objection被提起(raise_ objection),如果有,那么等待这个objection被撤销(drop_objection)后停止仿真;…

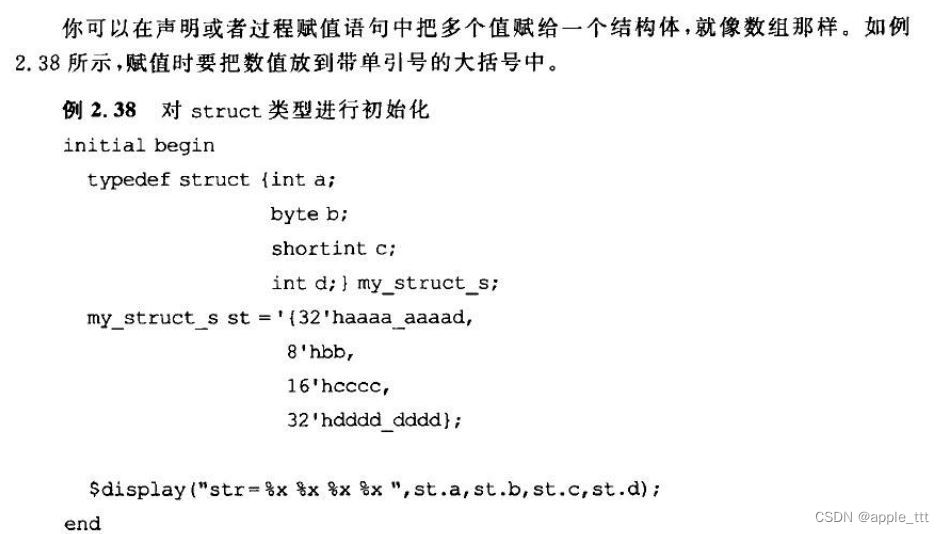

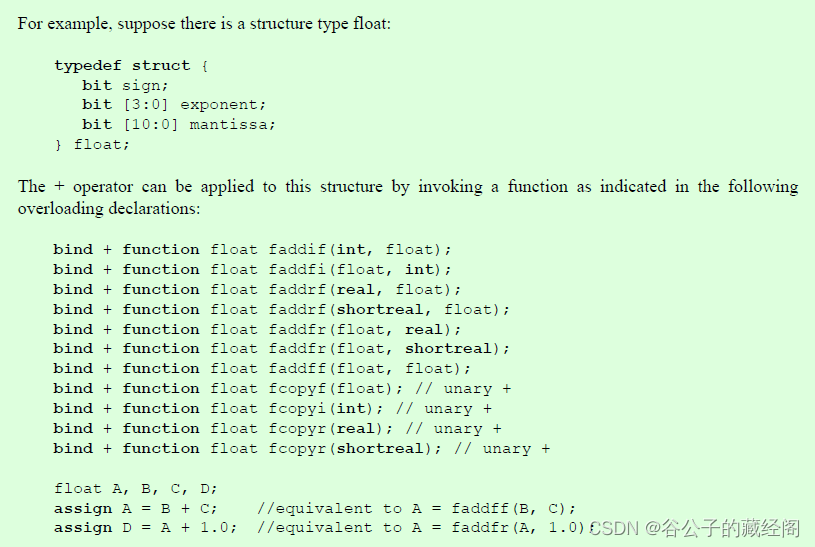

SystemVerilog学习(4)——自定义结构

一、 通过typedef来创建用户自定义类型 typedef语句可以用来创建新的类型。例如,你要求一个算术逻辑单元(ALU)在编译时可配置,以适应8比特、16比特,24比特或32比特等不同位宽的操作数。在Verilog中,你可以为操作数的位宽和类型分别定义一个宏(macro),如例2.32所示。 SV则提供了…

sv中的task和function

sv中的task和functiontask和function的共同点task和function的不同点task和function的共同点

verilog中task和function是相同的。将复杂代码分割成小段落,便于理解和调用,简化程序,功能单一;.端口参数默认都是输入,除…

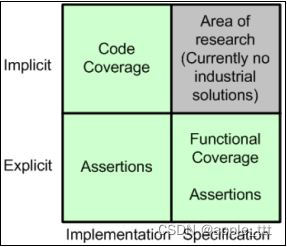

Systemverilog中Assertions的记录

1. assertion statement

Assertion statement有以下几种类型:

assert: 指定DUT的property,必须要verifyassume: 给验证环境指定假设的property。simulator检查这些property,但是formal工具会使用这些信息来产生输入激励。cover: 监控proper…

【IC萌新虚拟项目】spt_core模块基于dc的综合环境搭建与面积时序优化

关于整个虚拟项目,请参考: 【IC萌新虚拟项目】Package Process Unit项目全流程目录_尼德兰的喵的博客-CSDN博客 前言

当验证的同学正在疯狂写测试点,补充测试用例各种找茬找bug时候,设计的同学也要进入到跑综合修时序优化面积的阶段了。

还是老样子,关于芯片综合的知识就…

Systemverilog中array的记录

1. dynamic arrarys

Dynamic arrary是unpacked array,它的size是在run time时是可以改变的。动态数组的大小是通过new或者assignment来获得的。 2. Associative arrarys

动态数组适用于连续且size动态变化的情况。而关联数组(associative arrarys)可以用于需要存储…

苹果将允许第三方支付?你太天真了

程序员求职简历,项目经验怎么写?免费修改简历、提供模板并内部推荐昨天,偶然看到朋友转发一条说“苹果将开放第三方支付”的文章,我顿时心潮澎湃,我赶紧打开搜索引擎搜了一下。看到真的有很多自媒体大号都在报道这个事…

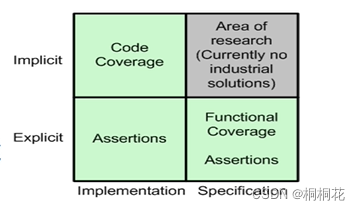

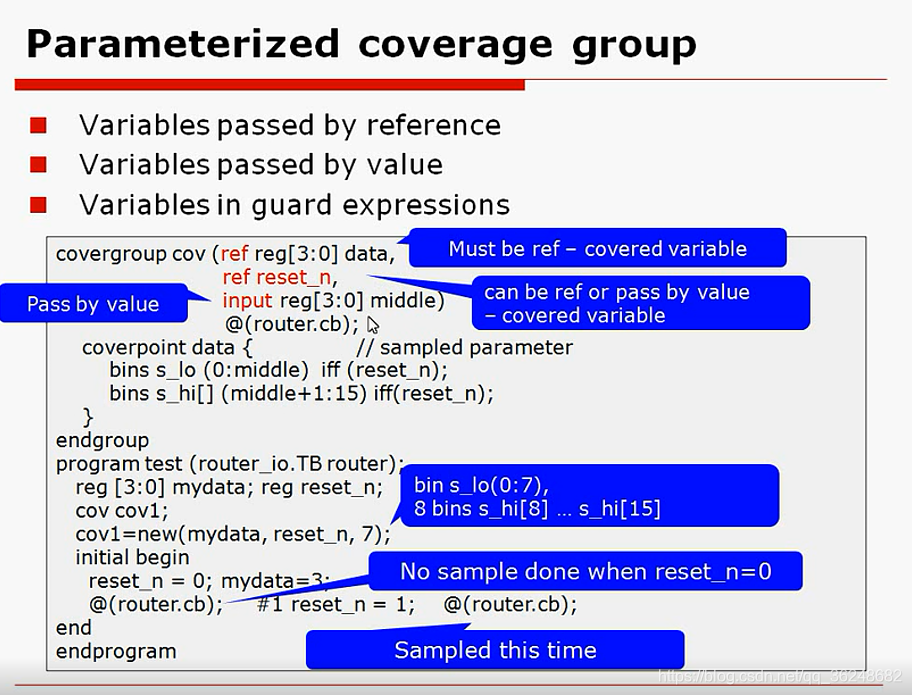

【路科V0】systemVerilog基础18——覆盖率

概述

“验证如果没有量化,那么就意味着没有尽头。” 伴随着复杂SoC系统的验证难度系数成倍增加,无论是定向测试还是随机测试,我们在验证的过程中终究需要回答两个问题:

是否所有设计的功能在验证计划中都已经验证?代码中的某些部分是否从未…

SystemVerilog interface详细介绍

1. Interface概念 System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。接口是将一组线捆绑起来,可以将接口传递给module。

2. 接口的优…

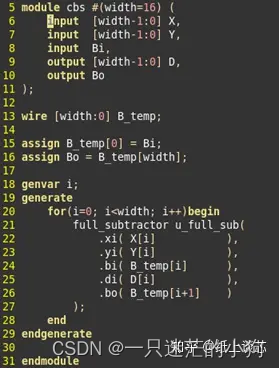

半减器、全减器和减法器原理和设计

减法器可由基础的半减器和全减器模块组成,或者基于加法器和控制信号搭建。定义N比特被减数X,减数Y,差为D(difference);来自低比特借位Bi,向高比特借位Bi1,i为比特序号;所以,有以下结…

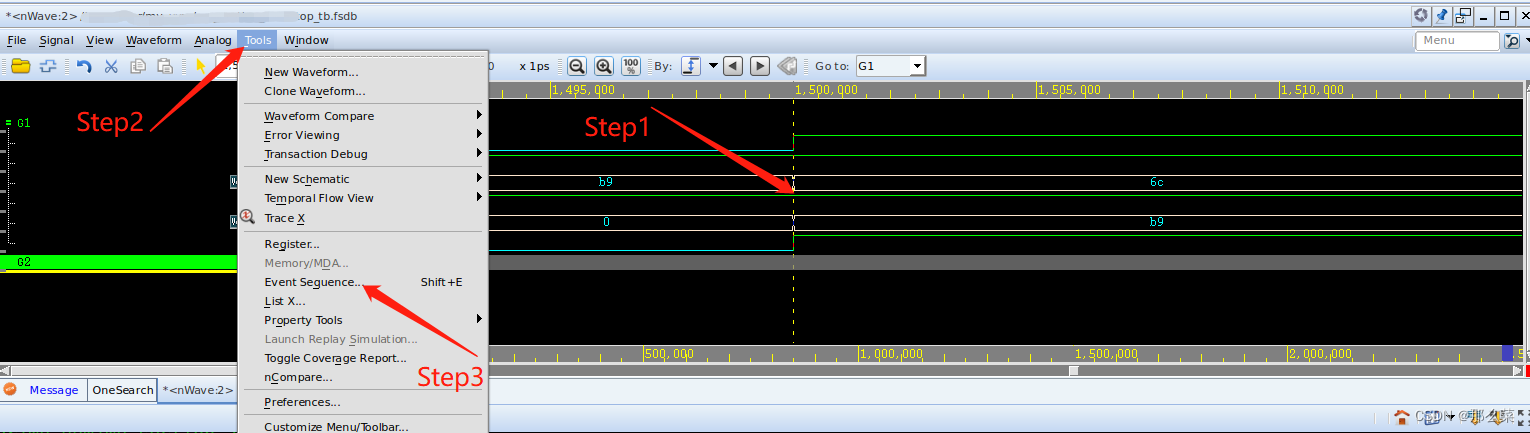

#systemverilog# 之 event region 和 timeslot 仿真调度(三)Verdi 辅助查看

前面的几篇文章,我们对SV仿真调度进行了理论分析和实战演练。那么工具厂商,对该类问题有没有提供相应的支持。这个应该是肯定的。因为我们知道,SV只是出于定义标准的角度,规定了仿真调度事件原理。但是具体实施细节,应是每家EDA仿真工具厂商根据自家的软件开发算法而定的。…

#systemverilog# 之 event region 和 timeslot 仿真调度(五)实战

目录

一 问题代码

二 解决方法

2.1 调换代码顺序

2.2 #0 Delay

2.3 uvm class 执行移到re-avtive

2.4 搭建完备的UVM 验证平台

三 预期波形 经过之前文章的学习,想必大家对systemverilog 仿真调度的理解,应该八九不离十了。今天,我们…

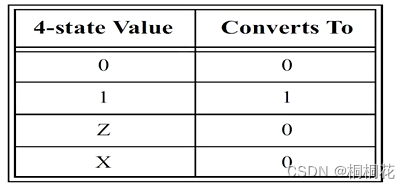

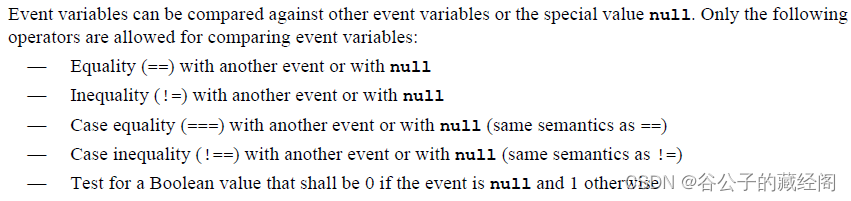

Systemverilog中operators和expression的记录

1. Equality operators

Equality operators有三种:

Logical equality:, !,该运算符中如果运算数包含有x/z态,那么结果就是x态。只有在两边的bit都不包含x/z态,最终结果才会为0(False)或1(True)Case equality…

【路科V0】systemVerilog基础16——线程的同步

概述 测试平台中的所有线程都需要同步并交换数据。(在测试平台中,不但设计层次的各个硬件模块实例在依靠信号做同步和数据交换,验证环境中的各个组件也需要做同步和数据交换。) 一个线程等待另外一个线程结束。验证环境中的同步和…

IEEE Standard for SystemVerilog—Chapter 25.7 Tasks and functions in interfaces

子例程(任务和函数)可以在接口中定义,也可以在连接的一个或多个模块中定义。这允许更抽象的建模级别。例如,“读”和“写”可以定义为任务,而不需要引用任何连线,主模块只能调用这些任务。在modport中&…

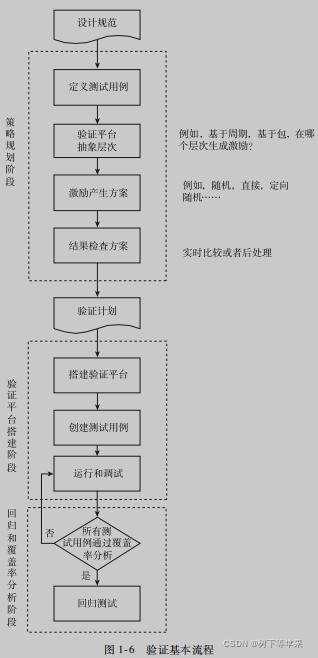

SystemVerilog与功能验证-学习笔记——第一章:功能验证技术与方法学概要(一)

功能验证技术与方法学概要(一)- 功能验证与验证平台 1.1 功能验证与验证平台1.1.1 专用芯片设计流程1.1.2 什么是验证1.1.3 验证平台可以做些什么1.1.4 功能验证流程本章从芯片设计流程入手,讨论功能验证在整个流程中的位置及其所涵盖的内容&…

Systemverilog里data type的记录

1. 区别data type和data object

我的理解data type是类似于class type,然后data object是类似于class object,相当于一个entity。所以data type可以用于声明data object。每一个data object是一个命名的entity,它带有一个data value和data t…

聊聊Systemverilog中的function in constraints

有些情况下,constraint不能简单用一行来表达,而是需要复杂的计算,如果都写到constraint block内部就比较复杂,而且很乱,这时候可以调用functions来约束随机变量。在constraint内调用function就称为”function in const…

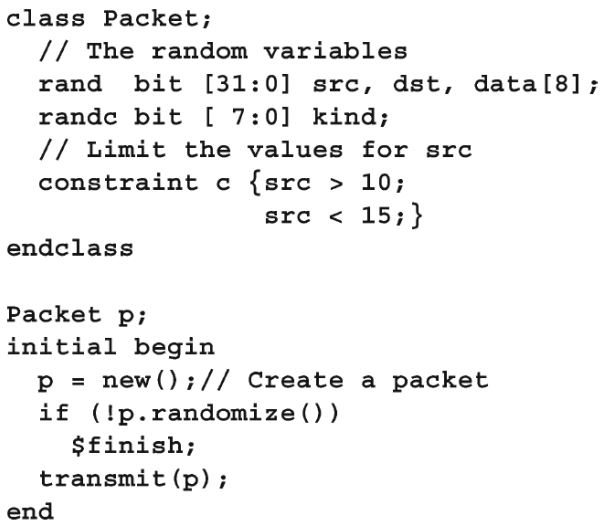

Systemverilog中Constrained random value generation的记录

1. constraints的一些重要属性

constraints可以是任何包括整型variables或整型constant的expression,如:bit, reg, logic, integer, enum, packed, struct.求解存在时返回正确的值,如果constraint过约束而导致误解,返回errorcons…

SystemVerilog学习(0)——目录与传送门

一、验证导论

SystemVerilog学习(1)——验证导论-CSDN博客文章浏览阅读403次。SystemVerilog自学,验证系统概述,什么是SVhttps://blog.csdn.net/apple_53311083/article/details/133953016

二、数据类型

SystemVerilog学习&…

Systemverilog中使用interface连接testbench和dut的端口

1.dut的端口声明如下,文件名为top.v:

module top

(input clk ,input rst_n ,input wr_n ,input rd_n ,input cs0_n ,input cs7_n ,input [15 : 0] bus_addr_in ,//UART淇″彿input rx0_d ,output tx0_d , …

支持寄存器模型读写功能的AHB driver实现——导读

1.前言

UVM driver在接口协议的实现中起着非常重要的作用,因为它一端处理基于类的事务级sequence,另一端处理基于时钟的信号/引脚级的总线行为。因此,如何实现 UVM driver及其与sequence的同步对于 DUT 和 UVM 环境之间的交互以及避免 UVM d…

SystemVerilog语法中,在Class中引用层次化信号

在class中可以像在verilog中一样,直接在class中引用层次化信号。示例如下: 1.DUT模块,文件名为top.v。

module top

(input clk ,input rst_n ,//总线信号 input wr_n ,input rd_n ,input cs0_n ,input cs7_n …

UVM产生异常激励的方法

在UVM中,产生异常激励的方法(以白皮书中源码为例) 在my_transaction中添加一个crc_err的标志位这样,在post_randomize中计算CRC前先检查一下crc_err字段,如果为1,那么直接使用随机值,否则使用真…

【SystemVerilog】数据类型(2)定宽数组和动态数组

目录

一、定宽数组

1.1定宽数组的声明和初始化

1.2常量数组

1.3数组的基本操作——for、foreach

1.4数组的比较和复制

1.5合并数组

二、动态数组 SV对数组分为两类:定宽数组和动态数组。

定宽数组,一般长度始终固定,且不存在重用性的…

【SystemVerilog】数据类型(4)队列、枚举

本篇文章对SV的其他数据类型进行介绍。包括:链表、队列、枚举、typedef重定义、用户自定义、常量、字符串。 目录

一、队列

二、枚举

三、字符串

四、其他 一、队列 SV 引进了一种新的数据类型——队列,它结合了链表和数组的优点。队列与链表相似&am…

【路科V0】systemVerilog基础15——线程控制

什么是线程 在SV中,可以认为 线程即独立运行的程序。 线程需要被触发,可以结束或者不结束。

举例: 在硬件module中的initial和always,都可以看做独立的线程,它们会在仿真0时刻开始,而选择结束或者不结束。…

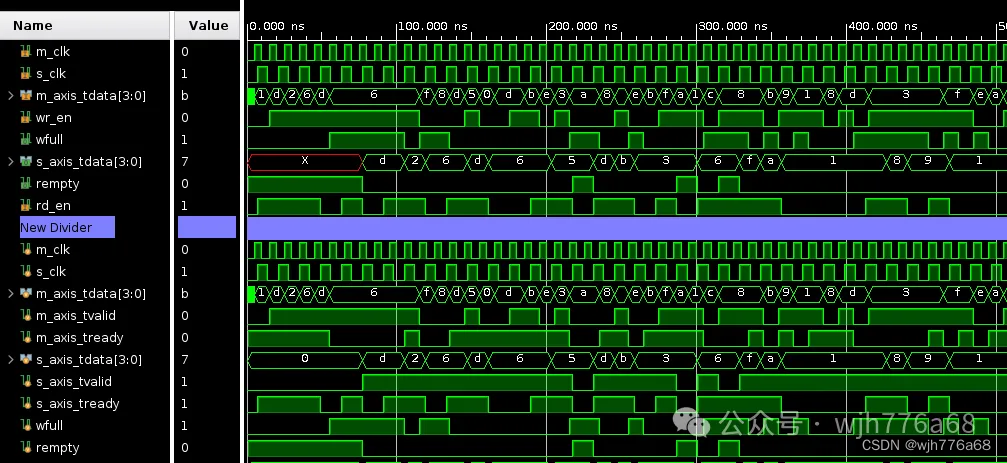

【AXIS】AXI-Stream FIFO设计实现(四)——异步时钟

前文介绍了几种同步时钟情况下的AXI Stream FIFO实现方式,一般来说,FIFO也需要承担异步时钟域模块间数据传输的功能,本文介绍异步AXIS FIFO的实现方式。 如前文所说,AXI-Stream FIFO十分类似于FWFT异步FIFO,推荐参考前…

【SystemVerilog】SV对Verilog的语法改进

SystemVerilog对Verilog兼容,就像C兼容C一样,前者是后者的超集。 目录

一、基本数据类型的改进

1.1SV对表示数字的语法改进

二、SV对设计意图的关键字细化

三、void函数

四、循环语句性能增强

五、隐含的端口连接

六、SV模块的接口 一、基本数据类…

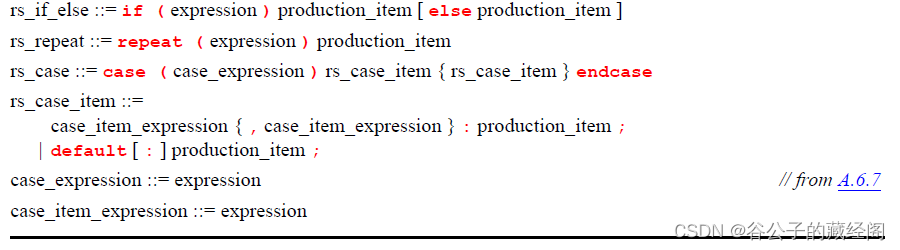

【SystemVerilog】SV对设计意图的细化always和unique/priority

always、always_comb、always_latch、always_ff;

unique /priority case ; unique /priority if...else ; 一、SV中的always

在Verilog中,设计组合逻辑和时序逻辑时,都要用到always:

always (*)begin…

【路科V0】systemVerilog基础17——线程的通信

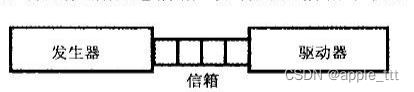

信箱mailbox 线程通信的三个类型:

eventsemaphoremailboxmailbox信箱,顾名思义,可以用来收发信息。 在SV中,mailbox可以用来存放任何数据类型,也可以从信箱中读取这些数据 信箱可以设置尺寸大小,防止存储数…

UVM1.2究竟在UVM1.1上做了哪些升级

想必大家平时也没有很注意UVM1.1版本和UVM1.2版本的不同之处,只有在用一些以前UVM1.1能支持的功能,到了UVM1.2却出现编译报错,找不到对应的变量或者函数或者类的时候,才意识到这两个版本的差异。笔者也是遇到了1个打印问题&#x…

dvt软件使用问题记录

首先将安装包解压缩到C:\dvt_eclipse(或自定义路径,我解压缩到D:\dvt_eclipse),然后复制license.dat到刚刚定义的路径中设置环境变量: DVT_HOMEC:\dvt_eclipse DVT_LICENSE_FILEFLEXLM DVTLMD_LICENSE_FILE…

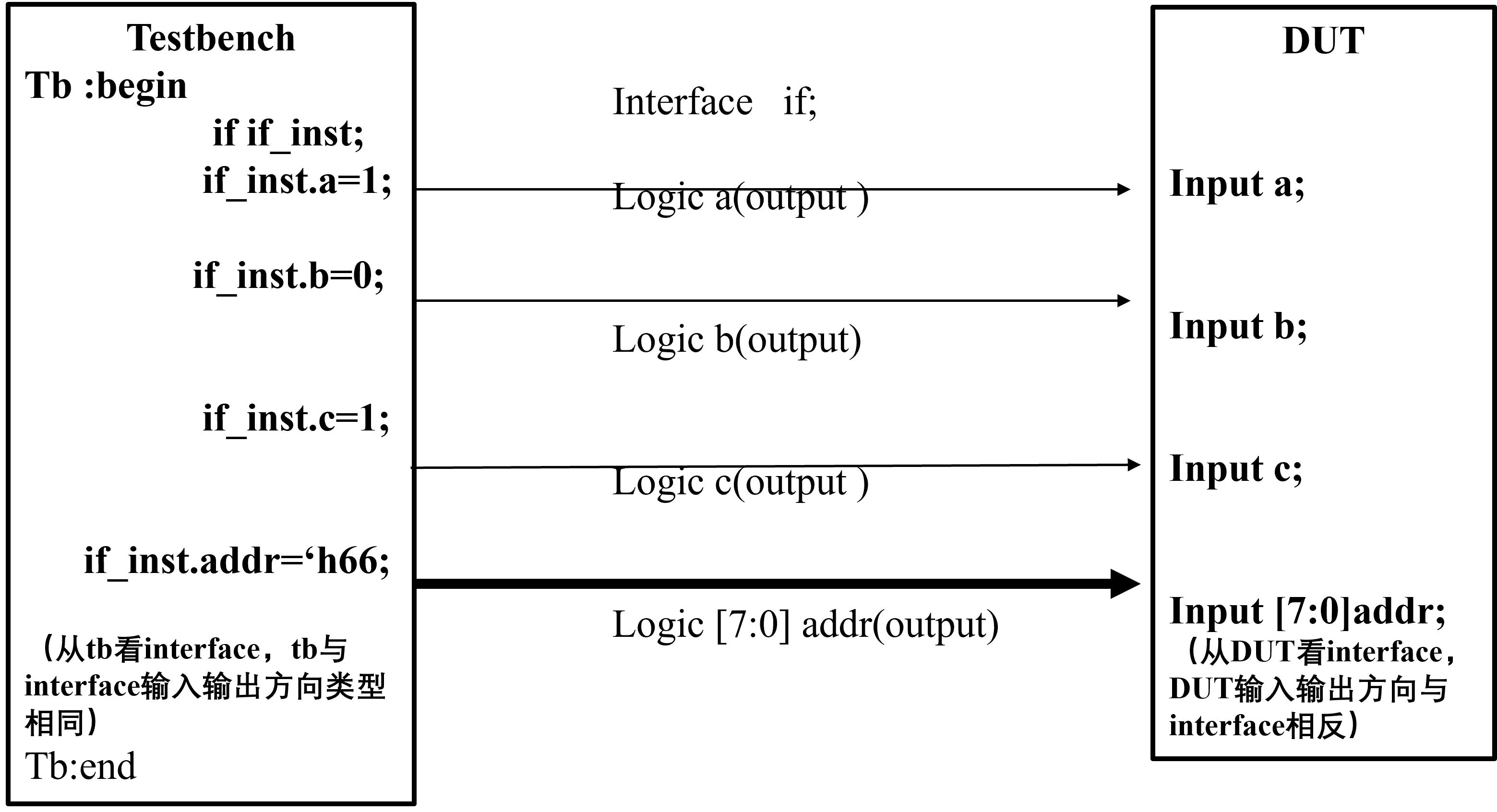

systemverilog:interface中端口方向理解

(1)从testbench的角度看,tb中信号的输入输出方向与interface中信号输入输出方向一致: (2)从DUT角度看,DUT中信号输入输出方向与interface中信号输入输出方向相反。简单图示如下:

代…

如果重复定义宏,两个值不同,最终的值是哪一个?

task F;

define AA 5 //定义一个宏,先编译

print(AA);

# 5; define AA 10 //重复定义宏,后编译

// 后面的值会覆盖前面定义的宏,但不是覆盖所有域,按照编译顺序,只覆盖该位置往后的域

print&…

SystemVerilog Chapter24: Programs

24.1General概述

本条款描述了以下内容: --Programs 声明 --Programs 调度语义 --与时钟块结合使用的Programs --匿名Programs

24.2 Overview module是设计的基本构建块。module可以包含其他模块、网络、变量、子例程声明以及a…

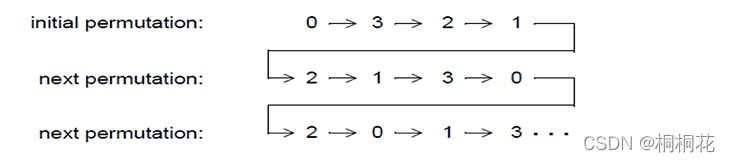

SystemVerilog学习 (9)——随机化

目录

一、概述

二、随机化

2.1、如何简单地产生一个随机数

2.1.1 利用系统函数产生随机数

2.1.2 urandom()

2.2、什么需要随机化

2.3、随机约束

2.3.1 rand 和 randc

2.3.2 随机约束的使用

2.3.3 约束块

三、总结 一、概述 随着设计变得越来越大,要产生一个完整的激…

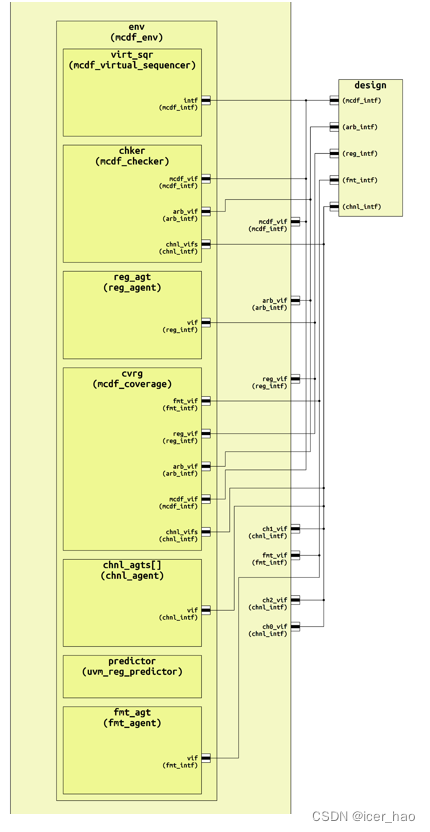

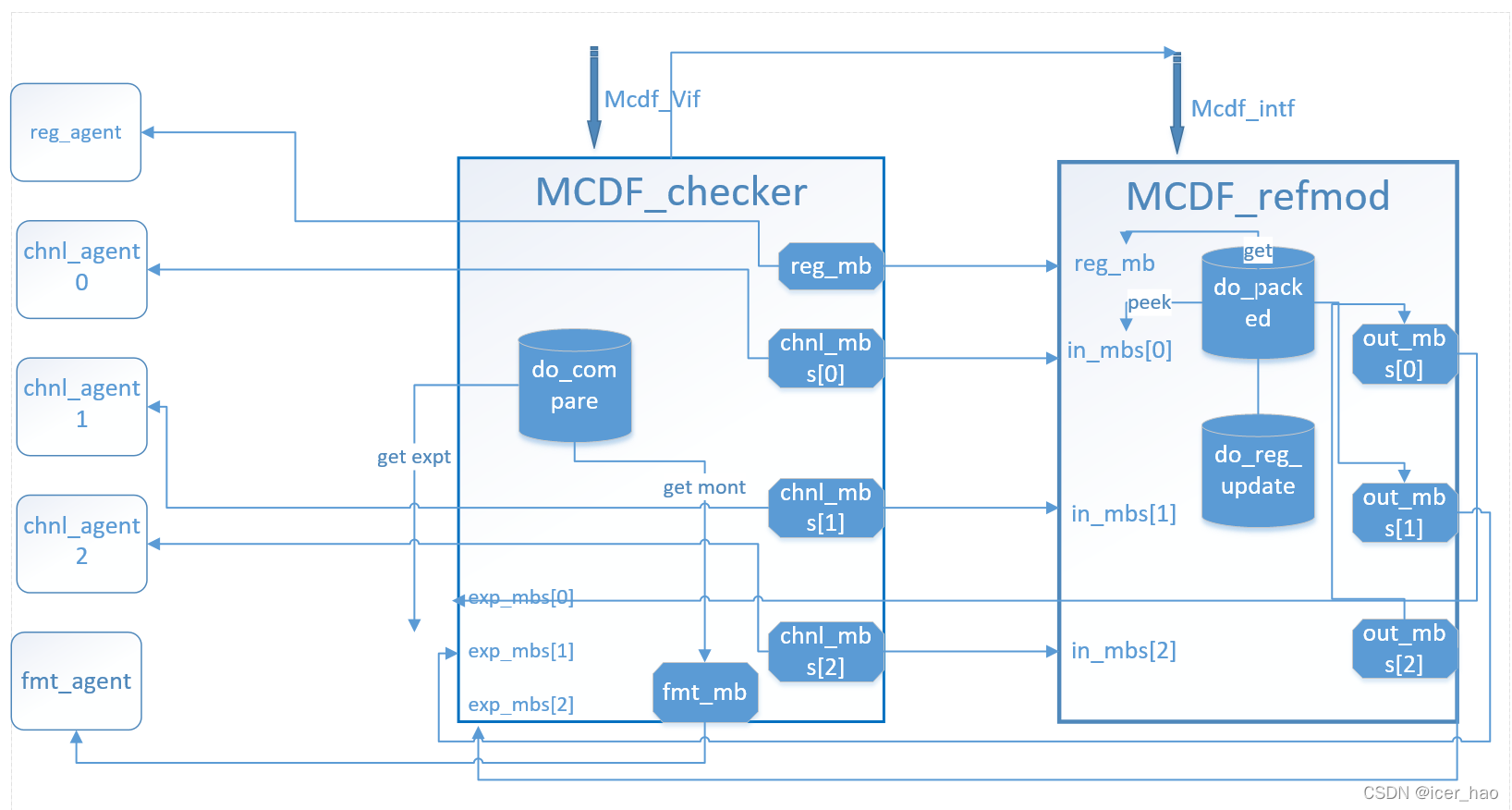

MCDF项目- mcdf_pkg代码层次梳理

功能介绍

在mcdf_pkg中,代码主要实现了checker功能,将从fmt_agent中得到的数据与经过refmod,把chnl_agent中数据经过packed以后的数据一起通过do_compare函数进行比对。refmod 模拟了硬件的行为,配置寄存器更新 并对chnl_agent中…

SystemVerilog学习 (5)——接口

一、概述 验证一个设计需要经过几个步骤: 生成输入激励捕获输出响应决定对错和衡量进度 但是,我们首先需要一个合适的测试平台,并将它连接到设计上。 测试平台包裹着设计,发送激励并且捕获设计的输出。测试平台组成了设计周围的“真实世界”,…

SystemVerilog学习(3)——数组

一、定宽数组 相比于Verilog-1995中的一维定宽数组,SV提供了更加多样的数组类型,功能上也大大增强。

1.1 定宽数组的声明与初始化 Verliog要求在声明中必须给出数组的上下界。因为几乎所有的数组都使用0作为索引下届,所以SV允许只给出数组的…

SystemVerilog 第5章 面向对象编程基础

5.1概述 对结构化编程语言,例如 Verilog和C语言来讲,它们的数据结构和使用这些数据结构的代码之间存在很大的沟壑。数据声明、数据类型与操作这些数据的算法经常放在不同的文件里,因此造成了对程序理解的困难。 Verilog程序员的境遇比C程序员更加棘手,因为Ⅴ erilog语言…

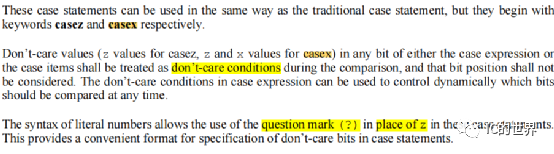

verilog语法之case casez casex

在rtl仿真中,有四种状态,分别是0、1、x(unknown values)和z(high-impedance values)。

case 结构体中:0,1,X与Z是四种不同的状态,case条件比较时会检测比较双…

【路科V0】systemVerilog基础13——约束控制

随机方法 在类中声明的随机变量,需要伴随着类句柄调用方法randomize(),这是SV类的内建方法:

virtual function int randomize(); 如果随机化成功则会返回1,如果失败则会返回0。

注意:

对象的例化和随机化是两件事,需…

【路科V0】systemVerilog基础4——接口类型

Verilog是通过模块之间进行端口连接来完成模块间通信的。对于大型设计,通过端口进行连接将会让硬件集成变得乏味和容易出错。SV在Verilog语言基础上扩展了接口(interface) 。 接口

接口(interface)的特点:

接口提供了一种新型的…

【路科V0】systemVerilog基础14——任务和函数

概述 类似于C语言,函数(function)和任务(task)可以提高代码的复用性和整洁度。 它们的目的都在于将大型的过程块切分为更细小的片段,而便于阅读和代码维护。 函数与任务之间有相同点和不同点。

函数function 函数的首要目的在于为…

【路科V0】systemVerilog基础2——自定义类型

自定义类型

通过用户自定义类型,以往Verilog的代码将可以通过更少的代码来表示更多的功能。 用户自定义类型使得代码的可读性更好。

自定义类型的方法:

通过typedef来创建用户自定义类型。通过enum来创建枚举类型。通过struct来创建结构体类型。

typ…

【路科V0】systemVerilog基础12——随机约束

带有随机变量的简单类 与之前定义的类不一样的地方,这里的类都具有随机属性 。这些随机属性,在类例化以后,可以通过类的随机化函数randomize()被随机化。

注意: randomize()随机化函数是系统预定义的,任何一个类都可以…

【路科V0】systemVerilog基础3——字符串类型

Verilog语言对于字符串的处理手段非常有限。SV引入了string类型用来容纳可变长度的字符串。 SV中字符串的特点: 字符串类型变量的存储单元为byte类型( 8位二值逻辑)。 字符串类型变量长度为N时,其字符成员索引值为从0到N-1…

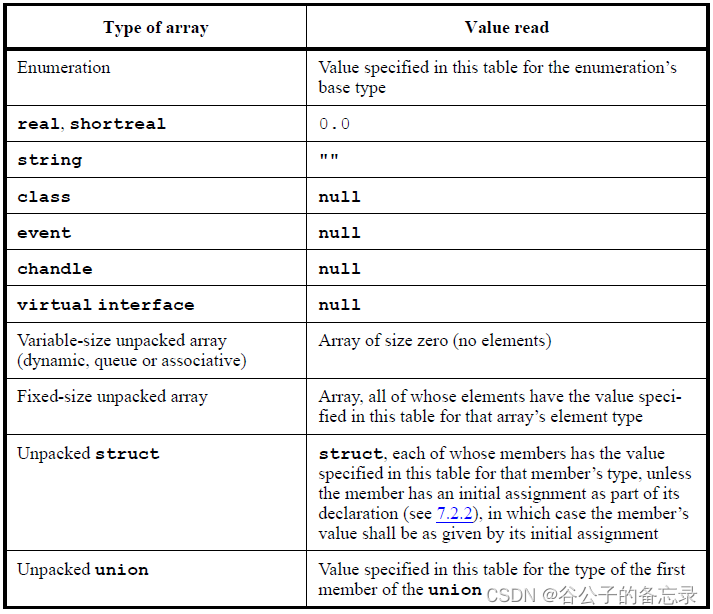

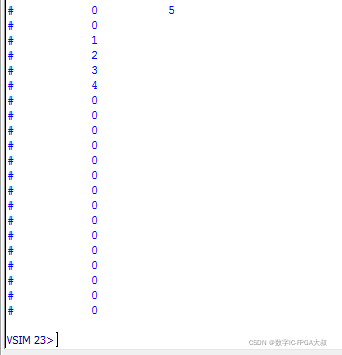

systemverilog 2 定宽数组

1. 数组的声明(一维和多维)

一维数组

int a[15];

二维数组

int a[16][5]; 当访问越界地址时,读出的数据会是默认值,4值逻辑,如logic会返回x,2值逻辑如bit会读出0,而wire在没有驱动的时候会输出Z(高阻态)

2. 定宽数组初始化

int a[5] = { 0,1,2,3,4}; // 加 花括…

SystemVerilog 控制流语句

unique-if/unique0-if 对于unique-if ,如果condition没有一个匹配且没有加else语句,则会报告一个错误;如果超过1个condition匹配,也会报告错误; unique0-if与unique-if的不同之处在于,如果没有一个conditi…

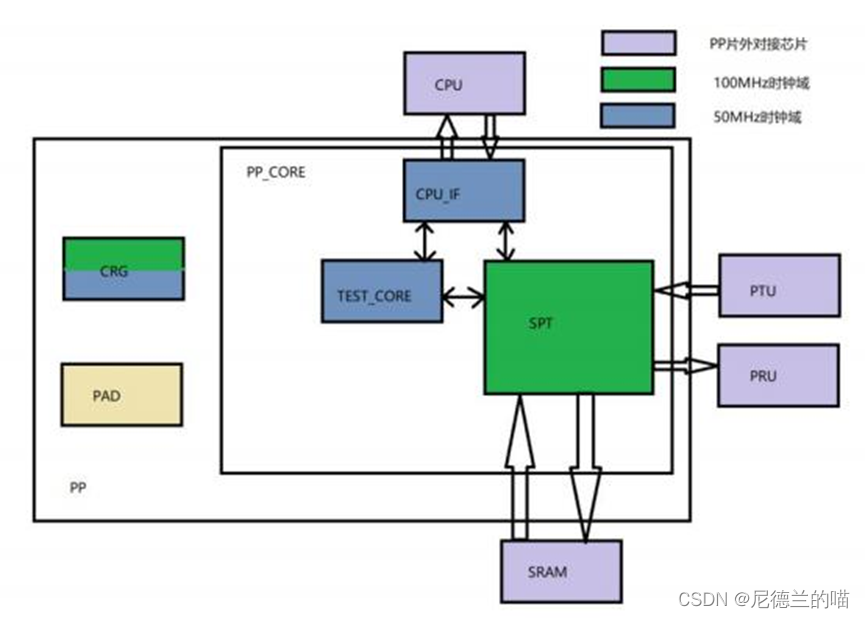

【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART2

4.系统功能和主要技术指标论证 4.1芯片总体结构图 芯片总体结构框图如图2所示。 图 2 packet_process_unit 芯片结构框图 芯片内部主要电路包括 cpu_if 接口电路、sram 检测电路 test_core 以及 spt 包转发接口电 路。以下对主要部分分别进行简要介绍:

1.cpu_if 接口电路

该…

【路科V0】systemVerilog基础11——随机变量

概述 随着设计变得越来越大,要产生一个完整的激励来测试设计的功能也变得越来越困难。 定向激励的测试方法早已经无法满足检查功能完整性的要求。 SoC的集成度提高带来的模块之间交互的复杂度也是指数攀升,这就使得验证工程师无法预测接下来用户使用过程…

【路科V0】systemVerilog基础1——数据类型

数据类型

Verilog语言两种基本的数据类型:

变量类型(variables)【reg,integer和time等变量类型可以用来存储组合逻辑或者时序逻辑的值。】线网类型(nets)【例如wire,wor,wand和其它线网类型用来连接硬件模块,以及提供特殊的线网驱动解决方案…

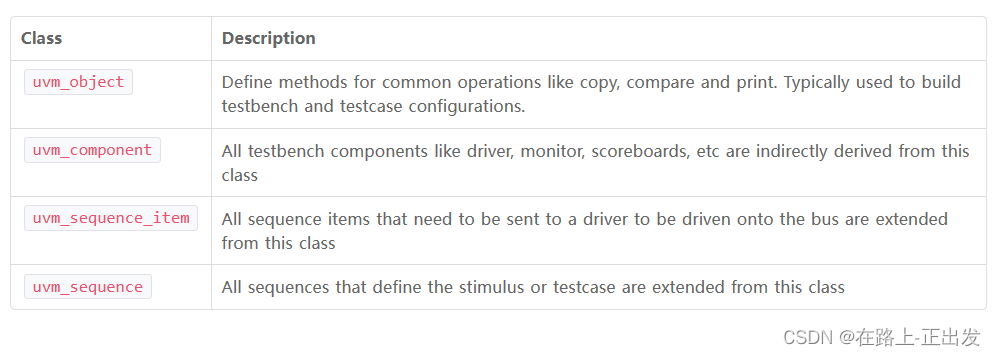

UVM-什么是UVM方法学

概念简介

百度对UVM的解释如下: 通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境 UVM…

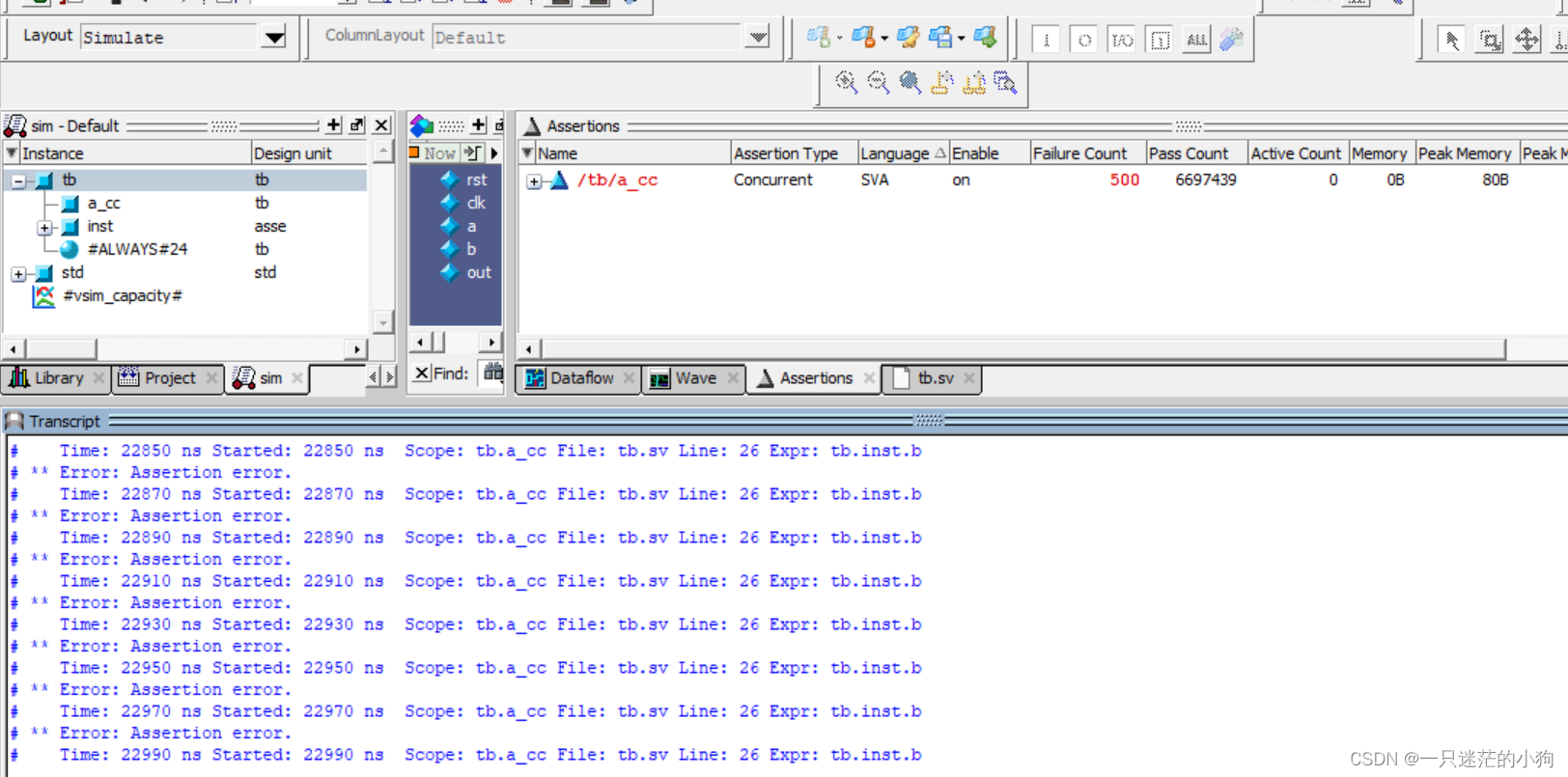

Modelsim查看断言

断言编译modelsim

在modelsim中开启断言编译和显示功能:

【编译verilog代码时按照system verilog进行编译】

vlog -sv abc.v 或者使用通配符编译所有的.v或者.sv文件 ( vlog -sv *.sv *.v)

【仿真命令加一个-assertdebug】

vsim -a…

vcs仿真教程(查看断言)

VCS是在linux下面用来进行仿真看波形的工具,类似于windows下面的modelsim以及questasim等工具,以及quartus、vivado仿真的操作。

1.vcs的基本指令

vcs的常见指令后缀 sim常见指令

2.使用vcs的实例

(1)新建文件夹: …

[SV]SystemVerilog二维关联数组使用案例

SystemVerilog二维关联数组使用案例 摘要:二维的关联数组是一种非常重要的数据结构,在验证环境中用于保存一些特定的对象,用于检索和分析。本文会介绍一种二维关联数组的使用案例。关于SystemVerilog关联数组的基础知识,请参考以下博文: Systemverilog關聯數組

前端设计跨异步处理手段

简单描述下笔者所了解的单bit和多bit信号跨时钟域处理的常见手段。

单bit信号跨时钟域处理手段

电平信号:可以直接打拍处理;脉冲信号(原始脉宽需保持至少2个DST时钟宽度):可以直接打拍处理,对同步后脉宽不…

#systemverilog# 关于流操作符>>和<<引发的思考

前言

对于流操作符,相比大家都不陌生,在实际项目中运用特别广泛。今天我们通过几个小例子,来回顾和深层认识一下该操作符。

概念

流操作符(bit-stream),表示方式为{>>{}} 和 {<<{}}。前者会…

Systemverilog中interprocess间synchronization和communication的记录

1. 同步和通讯机制的种类

systemverilog提供了三种方式:named event type(->, )、semaphore、mailbox。其中semaphores和mailbox虽然是built-in type,但它们是class,且可以作为base classes被扩展为更高level的class。这些built-in class…

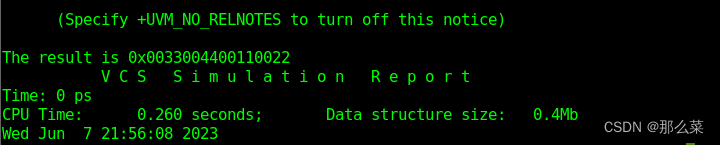

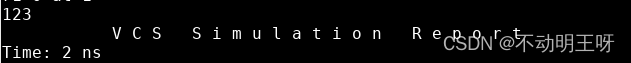

systemverilog运行的时候调用系统函数运行python等

systemverilog 运行的时候使用系统函数 使用场景,在仿真过程中,需要外部环境准备仿真参数,或者调整仿真参数的时候 创建一个python文件

print("123")创建一个sv文件

module dut ;initial begin$system("python 123.py"…

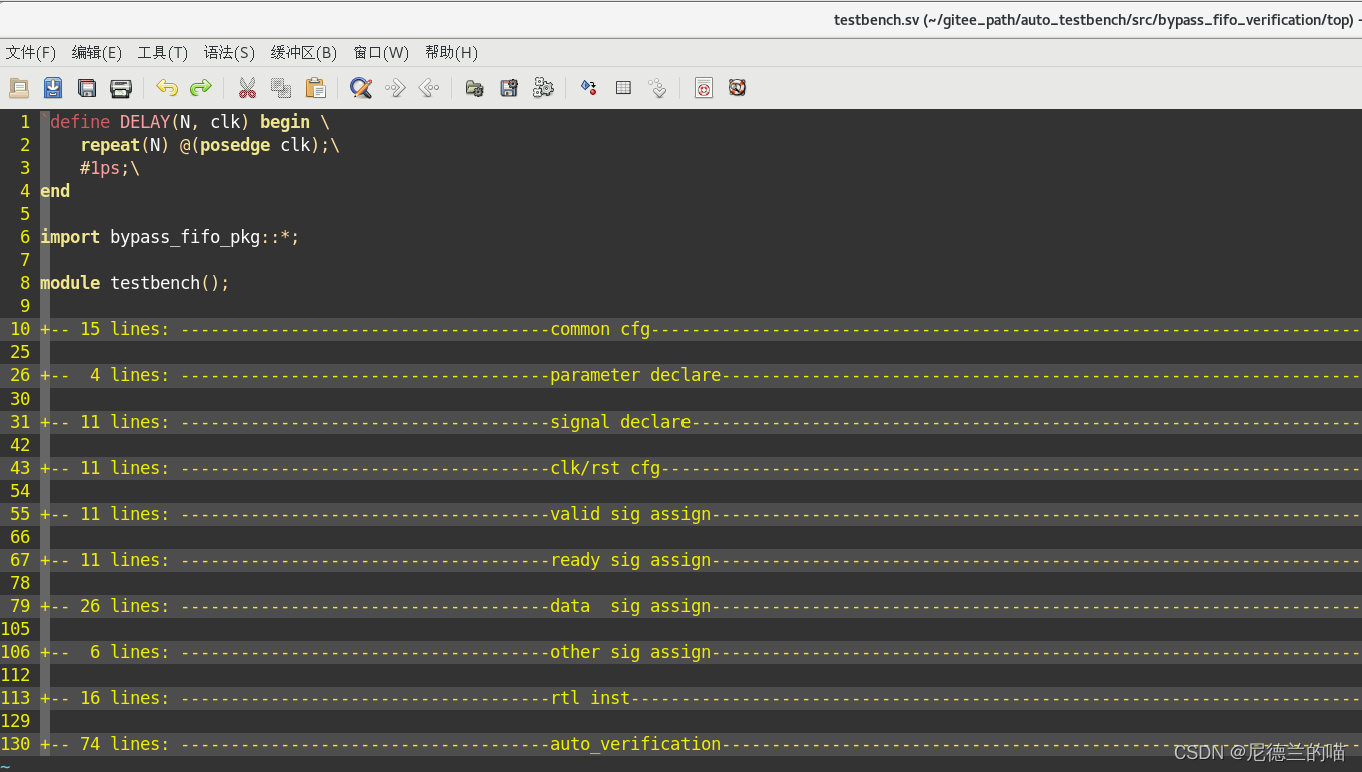

【芯片前端】auto_testbench的大版本升级——加入简单预期与自动比对

前言

前文提要:

【芯片前端】一键生成简易版本定向RTL验证环境的脚本——auto_verification_rtl脚本_尼德兰的喵的博客-CSDN博客

【芯片前端】可能是定向验证的巅峰之作——auto_testbench_autotestbench_尼德兰的喵的博客-CSDN博客

工具路径:

auto…

#systemverilog# 之 event region 和 timeslot 仿真调度(九)assign 赋值 和 always 组合赋值的调度区别

有时候,我们会发现一个问题,举个最简单的例子:比如将两个信号进行简单的异或运算。该逻辑运算,我们可以使用 assign 数据流建模完成,也可以使用always 组合逻辑过程赋值语句实现。那仿真工具在对它进行调度的时候,有什么区别吗?

不慌,今天,我们举个例子,来验证这一点…

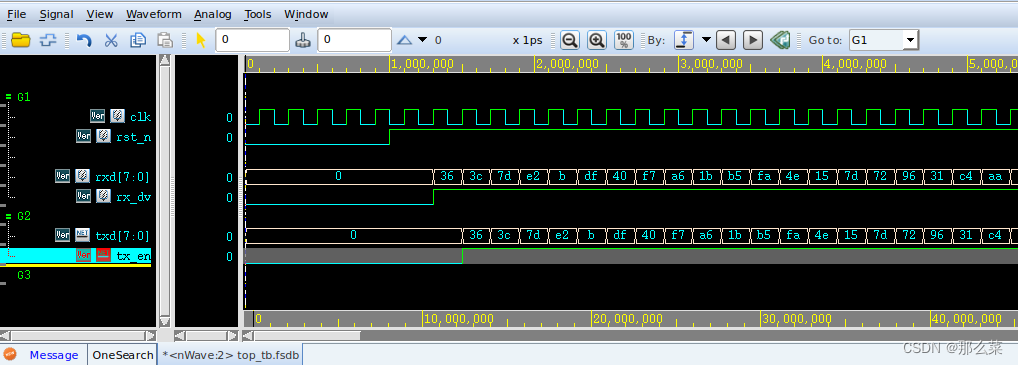

uvm白皮书练习_ch2_ch221只有driver的验证平台之*2.2.1 最简单的验证平台

uvm白皮书练习 ch221 dut.sv 这个DUT的功能非常简单,通过rxd接收数据,再通过txd发送出去。其中rx_dv是接收的数据有效指示,tx_en是发送的数据有效指示。

module dut (clk,rst_n,rxd,rx_dv,txd,tx_en

);input clk ; input rst_n ; in…

详解SystemVerilog中time slot的调度

1. 前言

本文讲一下SystemVerilog的time slot里的regions以及events的调度。SystemVerilog语言是根据离散事件执行模型定义的,由events驱动。SystemVerilog描述是由连接的执行thread或processes组成。Process是可衡量的,也具有状态,并且可以…

System Verilog学习笔记

System Verilog学习笔记之启芯教程

具体视频教程B站链接,点击可以观看 文章目录System Verilog学习笔记之启芯教程SystemVerilog 01 DUTSystemVerilog 02 TestbenchSystemVerilog 03 Language Basic oneSystemVerilog 05 Stimulus driven and receivedSystemVerilo…

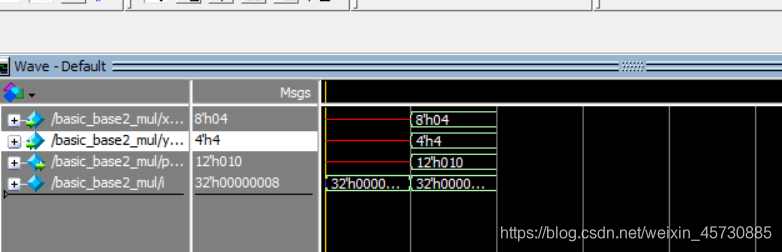

QuartusII和Modelsim联合仿真实现不带时钟信号的简单乘法器

创建项目 找个地方新建文件夹,设置这个项目的路径为那个文件夹,项目名字可以自己取(为了避免后面的不统一,建议和我取一样的) 从空项目创建 不用添加任何文件 选择开发板,我选择的是这个,然后ne…

SystemVerilog(2)——数据类型

一、概述 和Verilog相比,SV提供了很多改进的数据结构。它们具有如下的优点:

双状态数据类型:更好的性能,更低的内存消耗队列、动态和关联数组:减少内存消耗,自带搜索和分类功能类和结构:支持抽…

【EDA Tools】Spyglass 检查 Verilog 和 SystemVerilog 混合语言及 Lint 检查

目录 写在前面

读入设计

发现问题并解决

Lint 检查 写在前面

Spyglass可以用于检查混合设计中的语言互操作性和一致性问题。对于设计中包含多种硬件描述语言的情况,Spyglass 能够识别并解析其中的模块及其互连,并对其进行验证。例如,在包含 Verilog 和 VHDL 的混合设计中…

#systemverilog# 之 event region 和 timeslot 仿真调度(七)Active/NBA 咋跳转的?

目录

一 目的

二 案例分析

2.1 先Active域,后 NBA 域

2.2 先Active域,后 NBA 域,后NBA域

【HISI IC萌新虚拟项目】Package Process Unit模块整体方案·PART3

5. 模块方案说明

5.1CRG 模块方案说明

5.1.1简介

CRG 模块实现复位信号的滤抖功能,可滤除小于100ns的低电平复位毛刺,并对复位信号进行同步化处理。同时,对100MHz的输入时钟信号进行2分频,作为 CPU_IF模块和TEST_CORE模块的工作时钟。

5.1.2接口信号 信号位宽I/O描述

Systemverilog 中 program 和 module 的区别

1、 module和program相似之处

1.和module相同,program也可以定义0个或多个输入、输出、双向端口。

2.一个program块内部可以包含0个或多个initial块、generate块、specparam语句、连续赋值语句、并发断言、timeunit声明。

3.在program块中数据类型、数据声明、函…

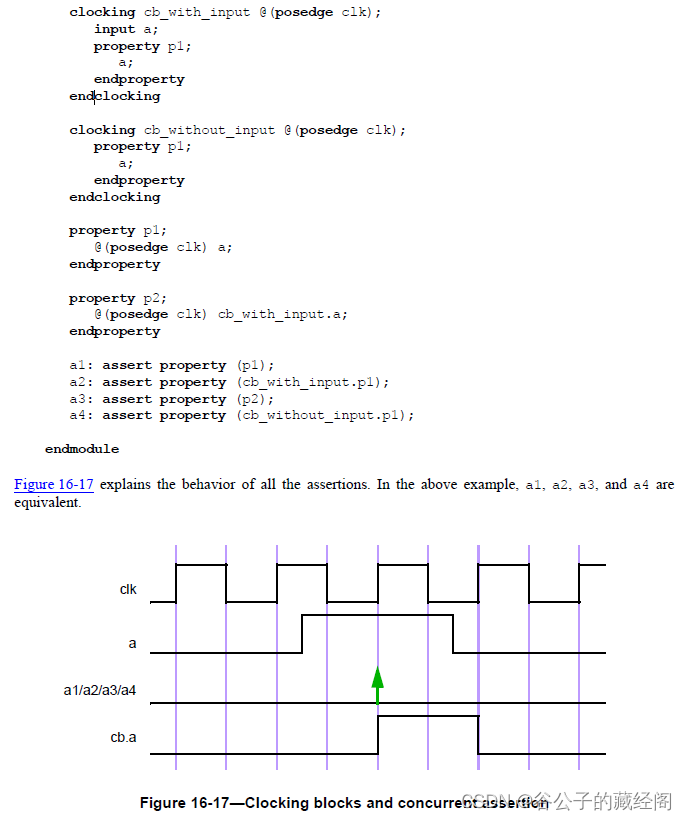

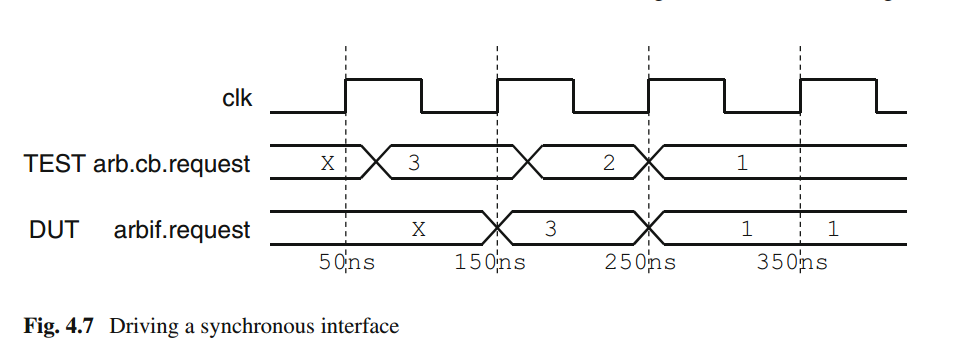

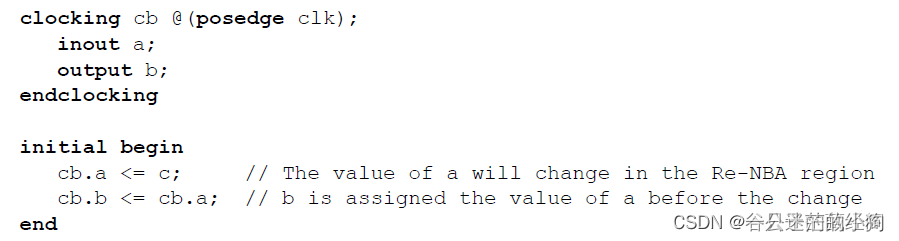

Systemverilog中Clocking blocks

1. clocking block的作用 Clocking block可以将timing和synchronization detail从testbench的structural、functional和procedural elements中分离出来,因此sample timming和clocking block信号的驱动会隐含相对于clocking block的clock了,这就使得对一些…

【SV中的多线程fork...join/join_any/join_none】

SV中fork_join/fork_join_any/fork_join_none 1 一目了然1.1 fork...join1.2 fork...join_any1.3 fork...join_none 2 总结 SV中fork_join和fork_join_any和fork_join_none; Note: fork_join在Verilog中也有,只有其他的两个是SV中独有的; 1 一目了然

1.…

systemverilog 中的always_comb, always_latch, always_ff

在verilog中,仅从alwasy关键字中不能直接看出设计者需要设计的是什么电路,为此SystemVerilog把always细化成always_comb, always_ff, 和always_latch。使综合工具可以自动检查各种细节,降低了设计失误的可能。

1:always_comb

al…

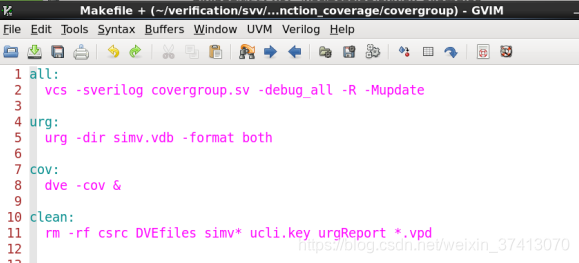

SystemVerilog基于覆盖率驱动验证技术(CDV)和生成-查看覆盖率报告

作者:小白蒋 所有的努力都是为了做个小白,单纯且快乐~ 本文内容基于覆盖率驱动的验证技术(CDV):代码覆盖率:断言覆盖率定义功能覆盖率模型covergroup解释功能覆盖率的采样事件定义覆盖点:bins定…

systemverilog中random用法-有符号数和无符号数-四值逻辑

作者:小白蒋 所有的努力都是为了做个小白,单纯且快乐~ 本文内容一、系统函数$random二、系统函数$random的用法1、$random % b2、{$random} % b三、有符号数和无符号数、四值逻辑一、系统函数$random

产生随机数,当函数被调用时,…

Cadence Xrun UVM Makefile

#记录工作实践

#基于Cadence Xrun工具的UVM Makefile

# #-- #-- File name : Makefile #-- Author : sh

#-- Date : 2023/11/01

#-- Abstract : Cadence Xcelium Xrun Makefile #-- # #############################################…

systemverilog/verilog文件操作

1、Verilog文件操作 Verilog具有系统任务和功能,可以打开文件、将值输出到文件、从文件中读取值并加载到其他变量和关闭文件。

1.1 、Verilog文件操作

1.1.1、打开和关闭文件

module tb;

// 声明一个变量存储 file handler

integer fd;

initial begin

// 以写权限打开一个文…

SystemVerilog学习 (11)——覆盖率

目录 一、概述

二、覆盖率的种类

1、概述

2、分类

三、代码覆盖率

四、功能覆盖率

五、从功能描述到覆盖率 一、概述 “验证如果没有量化,那么就意味着没有尽头。” 伴随着复杂SoC系统的验证难度系数成倍增加,无论是定向测试还是随机测试ÿ…

【SystemVerilog】数据类型(1)logic

相对于Verilog来说,SystemVerilog引进了一些新的数据类型,它们具有如下优点: (1)双状态数据类型:更好的性能,更低的内存消耗。 (2)队列、动态和关联数组:减少内存消耗,自带搜索和分类功能。 (3)…

SystemVerilog学习 (7)——面向对象编程

一、概述 对结构化编程语言,例如Verilog和C语言来讲,它们的数据结构和使用这些数据结构的代码之间存在很大的沟壑。数据声明、数据类型与操作这些数据的算法经常放在不同的文件里,因此造成了对程序理解的困难。 Verilog程序员的境遇比C程序员更加棘手,因为 Verilog …

SystemVerilog中的Program的学习笔记

1、SystemVerilog中的Program的作用? 将验证部分与设计部分进行隔离(实现方式就是将软件验证部分放置program中)2、SystemVerilog中的Program结束方式?

Program结束方式分为两种:1、隐式结束 2、显式结束

1、隐式结束…

SystemVerilog的数据类型

logic类型

logic是reg类型的改进,可以被过程赋值、连续赋值,门单元和模块所驱动。 编译器可自动推断logic是reg还是wire。 唯一的限制是logic只允许一个输入,不能被多重驱动,所以inout类型端口不能定义为logic。所以单驱动时用lo…

SystemVerilog学习 (10)——线程控制

一、概述 在实际硬件中,时序逻辑通过时钟沿来激活,组合逻辑的输出则随着输人的变化而变化。所有这些并发的活动在Verilog 的寄存器传输级上是通过initial和 always块语句、实例化和连续赋值语句来模拟的。为了模拟和检验这些语句块,测试平台使用许多并发执行的线程。在测试平台…

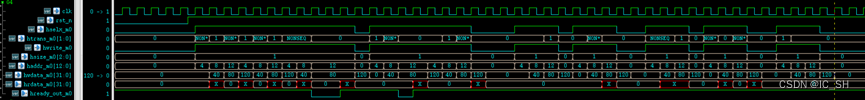

UVM项目笔记——通过寄存器模型实现AHB接口的寄存器读写(内含源码)

目录 1.前言

2.DRIVER实现

2.1 AHB二级流水时序

2.2 “队列错位法”实现driver

2.3 driver代码

2.4 仿真log与波形

2.5 多级流水拓展方法 1.前言

UVM driver在接口协议的实现中起着非常重要的作用,因为它一端处理基于类的事务级sequence,另一端处…

【RS422】基于未来科技FT4232HL芯片的多波特率串口通信收发实现

功能简介 串行通信接口常常用于在计算机和低速外部设备之间传输数据。串口通信存在多种标准,以RS422为例,它将数据分成多个位,采用异步通信方式进行传输。 本文基于Xilinx VCU128 FPGA开发板,对RS422串口通信进行学习。 根…

uvm白皮书练习_ch2_ch224_加入virtual interface

记录

参考使用uvm白皮书内容

从根本上来说,应该杜绝在验证平台中使用绝对路径

避免绝对路径一个方法是使用宏

define TOP top_tb

define TOP top_tb

task my_driver::main_phase(uvm_phase phase);phase.raise_objection(this);uvm_info("my_driver"…

UVM Heartbeat机制

1. 前言

在硬件电路中,为了使系统在异常情况下能自动复位,一般都需要引入看门狗(Watchdog)。看门狗其实就是一个定时器电路。当看门狗启动后,计数器开始自动计数,经过一定时间,如果没有被清零,计数器溢出就…