前言

对于流操作符,相比大家都不陌生,在实际项目中运用特别广泛。今天我们通过几个小例子,来回顾和深层认识一下该操作符。

概念

流操作符(bit-stream),表示方式为{>>{}} 和 {<<{}}。前者会把数据块按照从左到右的形式转化成bit流(stream),后者相反,则是从右到左形成一串数据流。

语法:

streaming_concatenation ::= { stream_operator [ slice_size ] stream_concatenation } // from A.8.1

stream_operator ::= >> | <<

slice_size ::= simple_type | constant_expression

stream_concatenation ::= { stream_expression { , stream_expression } }

stream_expression ::= expression [ with [ array_range_expression ] ]

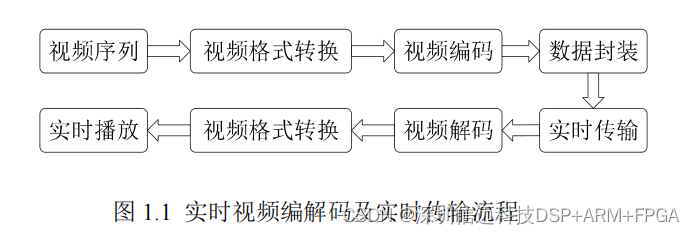

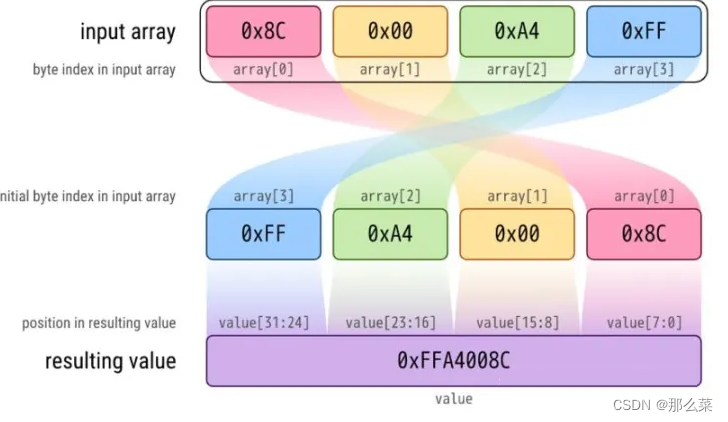

下面这个例子:实现了对数组内数据的逆序,并且将该数组打包为一个int。通过这句话我们知道,首先输入是一个数组,数组内含有多个元素;最终输出为一个int 数据。

语法解释:a = {<<byte{array}}

<1> {array} : 表示操作的对象是 一个数组指针

<2> << : 表示自右向左形成bit 数据流

<3>byte : 表示操作的对象的以byte == 8bit 为单位进行截取

原理图解释如下:

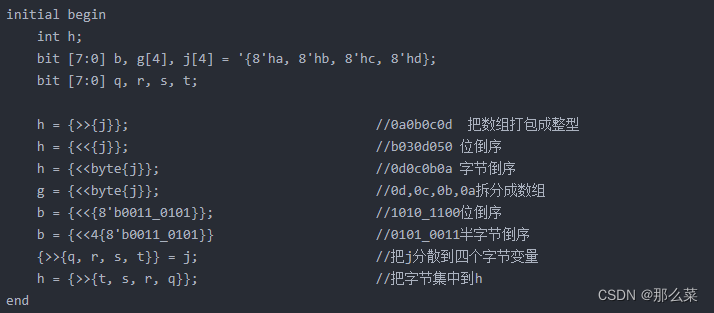

更多练习:

//a = {<<byte{array}}; // 例子默认以8 bit 为整体

//a = {<<{array}}; //0xff250031, 默认以单bit为整体

//a = {<<bit{array}}; //0xff250031, 以单bit为整体

//a = {<<bit[4]{array}}; //0xff4a00c8, 以4bit为整体

//a = {<<bit[3:0]{array}}; //0xff4a00c8, 以4bit为整体

//a = {<<bit[0:3]{array}}; //0xff4a00c8, 以4bit为整体

//a = {<<bit[0:2]{array}}; //0xfda44086, 以3bit为整体

//a = {<<logic[0:3]{array}}; //0xfda44086, 以4bit为整体

//a = {<<reg[0:3]{array}}; //0xfda44086, 以4bit为整体

//a = {<<bit[0:3]{array}}; //0xfda44086, 以4bit为整体

//a = {<<bit[16]{array}}; //0x0xa4ff8c00, 以16bit为整体

//a = {>>{array}}; //0x8c00a4ff , 以单bit为整体

//a = {>>bit{array}}; //0x8c00a4ff , 以单bit为整体

//a = {>>bit[4]{array}}; //0x8c00a4ff, 以4bit为整体

//a = {>>bit[8]{array}}; //0x8c00a4ff, 以8bit为整体

//a = {>>bit[2]{array}}; //0x8c00a4ff, 以2bit为整体

//a = {>>bit[3]{array}}; //0x8c00a4ff, 以3bit为整体

//a = {>>bit[5]{array}}; //0x8c00a4ff, 以5bit为整体

思考延伸

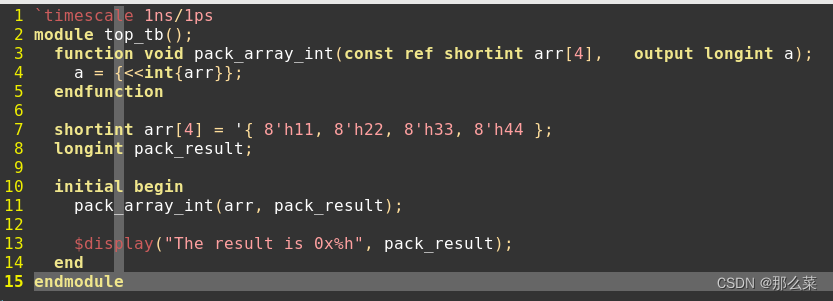

例子变形:

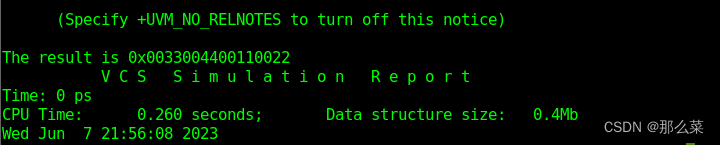

仿真输出结果如下:

因为我使用的计算机是64位的,所有对于int 数据类型内存占据 32bit, 而声明为 shortint 之后,变量内存占据16bit。故:

8'h11 -> 16'h0011

8'h22 -> 16'h0022

8'h33 -> 16'h0033

8'h44 -> 16'h0044

经过<<int(32bit)操作符之后,会以32bit 的方式形成bit 数据流。