相对于Verilog来说,SystemVerilog引进了一些新的数据类型,它们具有如下优点:

(1)双状态数据类型:更好的性能,更低的内存消耗。

(2)队列、动态和关联数组:减少内存消耗,自带搜索和分类功能。

(3)类和结构:支持抽象数据结构。

(4)联合和合并结构:允许对同一数据有多种视图(view)。

(5)字符串:支持内建的字符序列。

(6)枚举类型:方便代码编写,增加可读性。

双状态,即 0 / 1 ;而verilog中reg/wire都是四状态: 0 /1 /X /Z;

一、逻辑(logic)类型

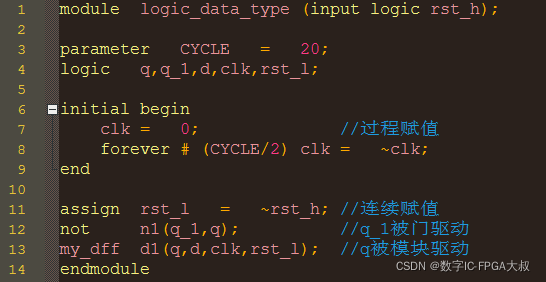

在Verilog中,初学者经常分不清reg和wire两者的区别。应该使用它们中哪一个来驱动端口?连接不同模块时又该如何做? SystemVerilog 对经典的reg数据类型进行了改进,使得它除了作为一个变量以外,还可以被连续赋值、门单元和模块所驱动。为了寄存器类型相区别,这种改进的数据类型被称为logic。任何使用线网的地方均可以使用logic,但要求logic不能有多个结构性的驱动,例如在对双向总线建模的时候。此时,需要使用线网类型,例如wire, SystemVerilog 会对多个数据来源进行解析以后确定最终值。

举个栗子:

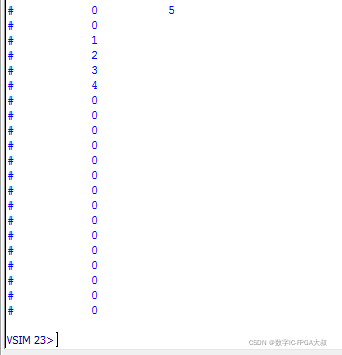

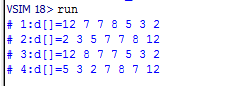

例1:

例2:

总结一下:

logic类型可以替代所有其他类型,包括reg类型。只有一个驱动源的变量都可以声明为logic类型。但是如果存在多个驱动,那么编译就会报错。

需要设计为多驱动的信号,例如双向总线,就需要定义为线网类型,例如wire。

二、双状态数据类型

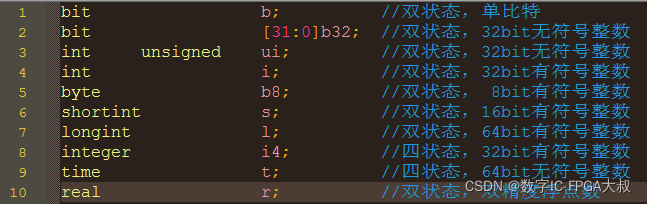

相比四状态数据类型,SV引入的双状态数据类型有利于提高仿真器的性能并减少内存的使用量。最简单的双状态数据类型是bit,它是无符号的。另四种带符号的双状态数据类型是byte,shortint,int,longint。如下所示:

需要注意的是:

- 新增的数据类型基本都是有符号的,使用时要注意。

- 在把双状态变量连接到被测设计,尤其是被测设计的输出时务必要小心。如果被测设计试图产生X或Z,这些值会被转换成双状态值,而测试代码可能永远也察觉不了。这些值被转换成了0还是1并不必要,重要的是要随时检查未知值的传播。使用($ isunknown )操作符,可以在表达式的任意位出现X或Z时返回1。