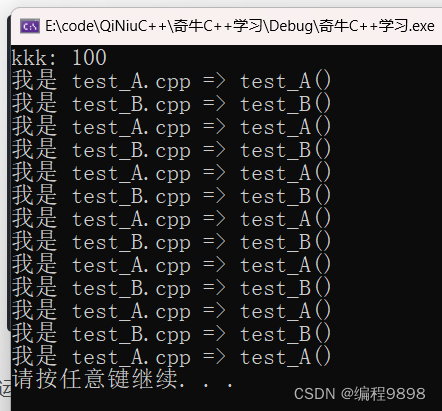

在class中可以像在verilog中一样,直接在class中引用层次化信号。示例如下:

1.DUT模块,文件名为top.v。

module top

(

input clk ,

input rst_n ,

//总线信号

input wr_n ,

input rd_n ,

input cs0_n ,

input cs7_n );

2.cpu类,文件名为cpu.sv,在cpu类中可以通过.运算符直接引用其他模块的信号,如tb.top_inst.syn_rst_n。

`include "tb_interface.sv"

class cpu;

virtual top_if cpu_if;//声明虚拟接口

function new(virtual top_if watch_dog_interface);//在构造函数中将虚拟接口传递到类变量中

cpu_if=watch_dog_interface;

endfunction

task signal_synchronous(logic [2:0] signal);

wait( tb.top_inst.syn_rst_n);//在类中直接引用其他模块的信号、变量

@(posedge tb.top_inst.sys_clk);

#1 ;

cpu_if.cs0_n<=signal[0];//通过接口对接口中的信号赋值

cpu_if.rd_n<=signal[1];

cpu_if.wr_n<=signal[2];

@(posedge tb.top_inst.sys_clk);

#1 ;

cpu_if.cs0_n<=signal[0];

cpu_if.rd_n<=signal[1];

cpu_if.wr_n<=signal[2];

@(posedge tb.top_inst.sys_clk);

#1 ;

cpu_if.cs0_n<=signal[0];

cpu_if.rd_n<=signal[1];

cpu_if.wr_n<=signal[2];

repeat(10) @(posedge tb.top_inst.sys_clk);

endtask

endclass3.在testbench中将dut和tb连接,并在tb模块中实例化类对象。

`timescale 1ns/1ps

`include "tb_interface.sv"

`include "watch_dog.sv"

`include "cpu.sv"

module tb;

bit clk ;

top_if topif(clk); //实例化top_if对象,将clk传递给interface

//top_if topif ;

dszj_2k_6001797_top top_inst( .clk(topif.clk), //将topif接口对象与DUT绑定,这里直接按照位置绑定

.rst_n( topif.rst_n ),

.wr_n(topif.wr_n),

.rd_n( topif.rd_n ),

.cs0_n( topif.cs0_n ),

.cs7_n(topif.cs7_n )

);

initial

begin

clk=0;

topif.rst_n=0;

#100 topif.rst_n=1;

end

always #12.5 clk=~clk;

watch_dog watch_dog_inst=new(topif);//将topif接口传递给watch_dog类的对象

cpu cpu_inst=new(topif);//将topif接口传递给cpu类的对象

initial

begin

repeat(1000) @(posedge clk);

watch_dog_inst.print();

// watch_dog_inst.

cpu_inst.signal_synchronous(3'b111);

end

endmodule

Leetcode 283.移动零和1089.复写零](https://img-blog.csdnimg.cn/img_convert/f1eaf0bc09739753935a317dfb2e5ad8.png)